# MODELING AND PERFORMANCE ANALYSIS OF DUAL MATERIAL DOUBLE GATE METAL OXIDE SEMICONDUCTOR FIELD EFFECT TRANSISTOR

# THIS THESIS IS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

HIMELI CHAKRABARTI

## MZU REGN NO : 1800282 PH.D REGN NO : MZU/PH.D./1287 of 27.07.2018

# DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING SCHOOL OF ENGINEERING AND TECHNOLOGY SEPTEMBER 2021

## MODELING AND PERFORMANCE ANALYSIS OF DUAL MATERIAL DOUBLE GATE METAL OXIDE SEMICONDUCTOR FIELD EFFECT TRANSISTOR

$\mathbf{B}\mathbf{Y}$

#### HIMELI CHAKRABARTI

Department of Electronics & Communication Engineering

Name of Supervisor : Dr. Niladri Pratap Maity

Submitted

In partial fulfillment of the requirement of the Degree of Doctor of Philosophy in Electronics and Communication Engineering of Mizoram University, Aizawl

Department of Electronics and Communication Engineering School of Engineering and Technology MIZORAM UNIVERSITY (A Central University) Tanhril, Aizawl – 796 004, Mizoram

#### **CERTIFICATE**

This is to certify that the thesis entitled "Modeling and Performance Analysis of Dual Material Double Gate Metal Oxide Semiconductor Field Effect Transistor" submitted to Mizoram University for the award of the degree of Doctor of Philosophy Electronics and Communication Engineering by Himeli Chakrabarti, Ph.D. Registration No. MZU/Ph.D./1287 of 27.07.2018, is Ph.D scholar in the Department of Electronics and Communication Engineering, under my guidance and supervision and has not been previously submitted for the award of any degree in any Indian or foreign University. She has fulfilled all criteria prescribed by the UGC (Minimum Standard and Procedure governing Ph.D. Regulations). She has fulfilled the mandatory publication (Publication enclosed) and completed Ph.D. course work. It is also certified that the scholar has been admitted in the Department through an entrance test, followed by an interview as per UGC Regulation of 2016.

Date: September, 2021 Place : Aizawl (Dr. Niladri Pratap Maity) Supervisor

#### MIZORAM UNIVERSITY Aizawl -796 004

#### September 2021

#### DECLARATION

I, Himeli Chakrabarti, hereby declare that the subject matter of this thesis entitled "Modeling and Performance Analysis of Dual Material Double Gate Metal Oxide Semiconductor Field Effect Transistor" is the record of work done by me, that contents of this thesis did not form basis of the award of any previous degree to me or to do the best of my knowledge to anybody else, and that the thesis has not been submitted by me for any research degree in any other University/Institute.

This is being submitted to the Mizoram University for the degree of Doctor of Philosophy in **Electronics and Communication Engineering.**

Date:

(Himeli Chakrabarti) **Candidate**

(Dr. Niladri Pratap Maity) Supervisor

(Dr. Niladri Pratap Maity) Head of the Department

#### Acknowledgement

At the outset, I express my gratitude to the almighty God for his grace, which has enabled me to complete my task successfully. I wish to express my heartfelt gratitude to my supervisor and mentor **Dr. Niladri Pratap Maity**, the Head of Department of Electronics and Communication Engineering, MZU, for his constant support, guidance, encouragement and patience throughout my research work. I am also thankful to **Dr. Reshmi Maity**, Associate Professor, for extending all the facilities. I am also thankful to all the faculties and technical staff of the department for their help, support and kind cooperation.

I would like to express my deepest gratitude to **Pulak Mazumder**, HOD of ECE department and all colleagues of Regent Education and Research Foundation Group of Institutions for their kind support, without whom, this work would not have been possible.

I would like to express my deepest gratitude to my colleagues, Avik Ghosh Dastidar, Dr. Rajdeep Chakravarty, Dr. Anindita Das, Dr. Dipankar Biswas and Suparna Panchanan for providing opportunity and constant support so that I can manage my responsibilities in my working sector and do my research work to complete Ph.D. I am grateful to Dr. Moumita Pal for her recommendations and assistance, which have aided me in numerous parts of my job.

Also, I would like to thank my parents, **Sitanshu Narayan Chakrabarti** and **Madhumita Chakrabarti**, parents in law, **Baidyanath Saha** and **Purabi Saha**, husband, **Partha Saha**, daughter **Doivangee Saha** and son **Deeptagni Saha** for their constant support, love and prayers. Last but not the least; I place on record, my sense of gratitude to one and all who, directly or indirectly, have lent their helping hand in this venture.

HIMELI CHAKRABARTI

## **Table of Content**

| Contents          |                |                                                                     | Page No |  |  |

|-------------------|----------------|---------------------------------------------------------------------|---------|--|--|

| Acknowledgme      | ent            |                                                                     | i       |  |  |

| Table of Contents |                |                                                                     |         |  |  |

| List of Figures   |                |                                                                     | v-viii  |  |  |

| List of Tables    |                |                                                                     | ix      |  |  |

| Chapter 1. Intro  | oduction       |                                                                     | 1-27    |  |  |

| 1.1               | Overview of    | MOSFET                                                              | 1       |  |  |

| 1.2               | Sketch on M    | OSFET- Scaling                                                      | 3       |  |  |

| 1.3               | Limitations of | of scaling effects                                                  | 6       |  |  |

| 1.4               | Short geomet   | try effects due to scaling                                          | 8       |  |  |

|                   | 1.4.1 Short cl | hannel effects                                                      | 8       |  |  |

|                   | 1.4.1.1        | Threshold voltage roll off                                          | 8       |  |  |

|                   | 1.4.1.2        | Sub threshold swing                                                 | 9       |  |  |

|                   | 1.4.1.3        | Drain induces barrier lowering                                      | 10      |  |  |

|                   | 1.4.1.4        | Channel length modulation                                           | 10      |  |  |

|                   | 1.4.1.5        | Velocity saturation                                                 | 11      |  |  |

|                   | 1.4.1.6        | Gate oxide leakage                                                  | 11      |  |  |

|                   | 1.4.2 Narrow   | channel effects                                                     | 12      |  |  |

|                   | 1.4.2.1        | Gate induce drain leakage                                           | 12      |  |  |

|                   | 1.4.2.2        | Fringing field effects                                              | 13      |  |  |

|                   | 1.4.2.3        | Hot carrier effects                                                 | 13      |  |  |

|                   | 1.4.2.4        | Impact ionization                                                   | 14      |  |  |

|                   | 1.4.2.5        | Parasitic BJT effects                                               | 15      |  |  |

| 1.5               |                | chnology-evaluation                                                 | 16      |  |  |

|                   |                | t and operation of dual material gate SOI MOSFET                    | 18      |  |  |

|                   | 1.5.2 Concep   | t and operation of graded channel<br>aterial double gate SOI MOSFET | 20      |  |  |

| 1.6               | High-k mater   | rials-its advantages                                                | 22      |  |  |

|                   | 1.6.1 Hafniur  | n dioxide and gate stack concept                                    | 23      |  |  |

| 1.7               | Scope of stud  | ły                                                                  | 24      |  |  |

| 1.8               | Thesis organi  | isation                                                             | 25      |  |  |

| Chapter 2 | DM   | DG MOSFET-A Review                                         | 28-39   |

|-----------|------|------------------------------------------------------------|---------|

|           | 2.1  | Overview of semiconductor technology                       | 28      |

|           | 2.2  | Significance of MOSFET parameters                          | 34      |

|           | 2.3  | Scaling limits of SiO <sub>2</sub>                         | 36      |

|           | 2.4  | High-k materials                                           | 37      |

| Chapter 3 | Surf | ace Potential and Electric Field of DMDG                   | 40-66   |

|           | 3.1  | Introduction                                               | 40      |

|           | 3.2  | Analytical model of surface potential of DMDG MOSFET       | 41      |

|           |      | 3.2.1 Boundary conditions                                  | 44      |

|           |      | 3.2.2 Solution of partial differential equation            | 51      |

|           | 3.3  | Results and discussions                                    | 55      |

|           | 3.4  | Summary                                                    | 65      |

| Chapter 4 | Surf | ace Potential and Electric Field of GCDMDG                 | 67-90   |

|           | 4.1  | Introduction                                               | 67      |

|           | 4.2  | Analytical Model for Surface Potential of GCDMDG MOSFET    | 69      |

|           |      | 4.2.1 Solution of partial differential equation            | 77      |

|           | 4.3  | Results and Discussions                                    | 81      |

|           | 4.4  | Summary                                                    | 90      |

| Chapter 5 | Thre | eshold Voltage                                             | 91-122  |

|           | 5.1  | Introduction                                               | 91      |

|           | 5.2  | Analytical Model for Threshold Voltage for DMDG MOSFET     | 93      |

|           | 5.3  | Analytical Model of Threshold Voltage for<br>GCDMDG MOSFET | 98      |

|           | 5.4  | Results and Discussions                                    | 103     |

|           | 5.5  | Summary                                                    | 122     |

| Chapter 6 | Drai | n Current                                                  | 123-144 |

|           | 6.1  | Introduction                                               | 123     |

|           | 6.2  | Analytical Model for Drain Current of DMDG MOSFET          | 125     |

|                           | 6.3  | Analytical Model for Drain Current of GCDMDG MOSFET | 128     |

|---------------------------|------|-----------------------------------------------------|---------|

|                           | 6.4  | Results and Discussions                             | 130     |

|                           | 6.5  | Summary                                             | 144     |

|                           |      |                                                     |         |

| Chapter 7                 | Cone | clusion and Future Scope                            | 145-149 |

|                           | 7.1  | Conclusion                                          | 145     |

|                           | 7.2  | Future Scope                                        | 148     |

| References                | 5    |                                                     | 150-170 |

| List of Pub               | 171  |                                                     |         |

| Bio Data of the Candidate |      |                                                     |         |

| Particular of Candidate   |      |                                                     |         |

# List of Figures

| Fig. No. | Figure Description                                                                                                                                                                                             | Page No. |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

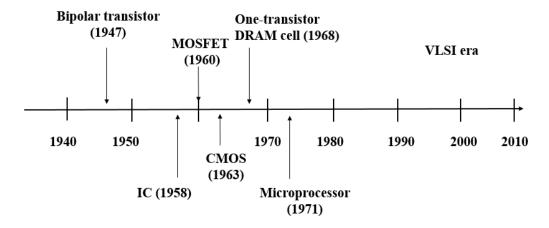

| Fig.1.1  | A brief chronology of the development in VLSI                                                                                                                                                                  | 2        |

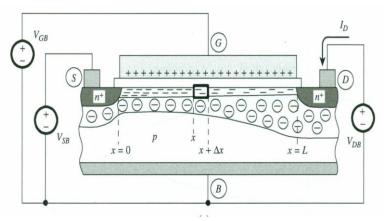

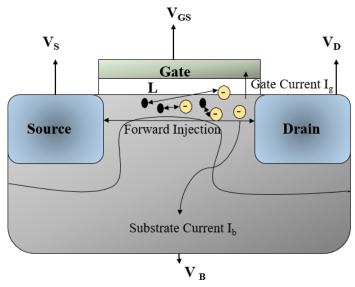

| Fig.1.2  | Cross-sectional view of a 4 terminals planar MOSFET                                                                                                                                                            | 2        |

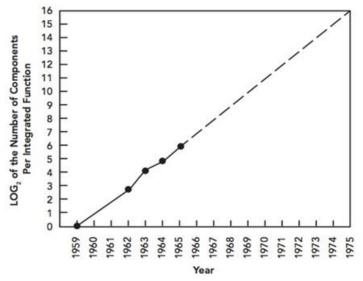

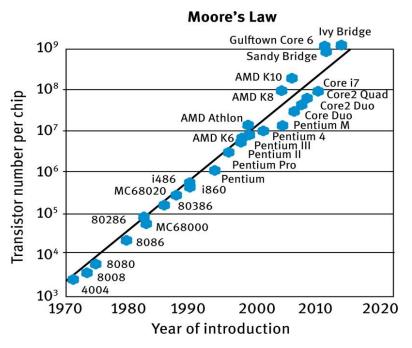

| Fig.1.3  | Moore's original 1965 Graph                                                                                                                                                                                    | 4        |

| Fig.1.4  | Recent trends in semiconductor industry according to Moore's Law                                                                                                                                               | 5        |

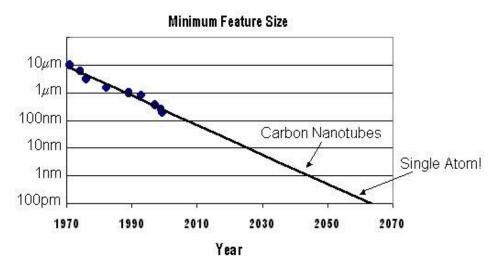

| Fig.1.5  | Component size over the time period                                                                                                                                                                            | 5        |

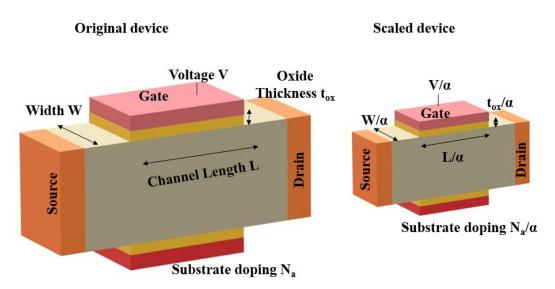

| Fig.1.6  | Scaling down Process                                                                                                                                                                                           | 6        |

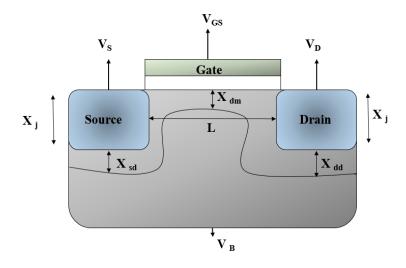

| Fig.1.7  | Cross sectional view of MOSFET with depletion region                                                                                                                                                           | 8        |

| Fig.1.8  | Cross sectional view of MOSFET shows depletion charge sharing                                                                                                                                                  | 9        |

| Fig.1.9  | Conduction energy band edge at the surface along<br>longitudinal direction for short channel MOSFET (a)<br>equal to flat band voltage and is 0V, (b) Strong inversion<br>mode, (c) strong inversion with large | 10       |

| Fig.1.10 | Schematic representation of CLM                                                                                                                                                                                | 11       |

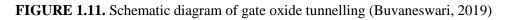

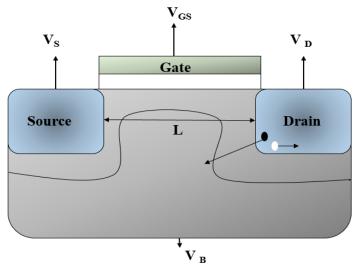

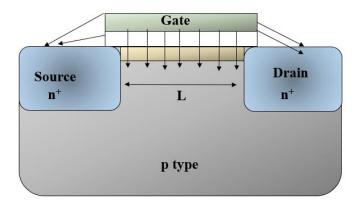

| Fig.1.11 | Schematic diagram of gate oxide tunnelling                                                                                                                                                                     | 12       |

| Fig.1.12 | Schematic diagram of GIDL effect                                                                                                                                                                               | 13       |

| Fig.1.13 | Cross sectional view of short channel MOSFET with fringing lines                                                                                                                                               | 14       |

| Fig.1.14 | Cross sectional view of MOSFET with hot electrons                                                                                                                                                              | 14       |

| Fig.1.15 | Cross sectional view of MOSFET showing impact ionization                                                                                                                                                       | 15       |

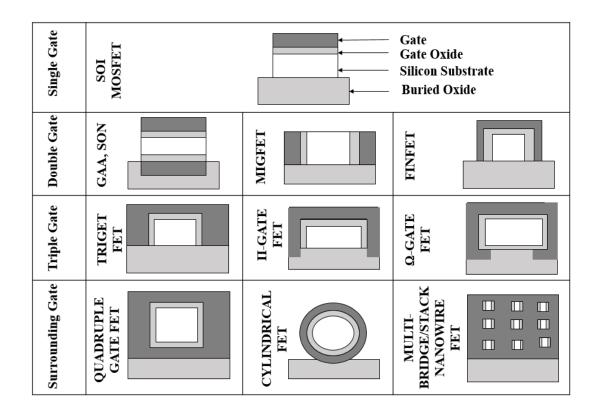

| Fig.1.16 | Possible devices with multi-gate structure                                                                                                                                                                     | 17       |

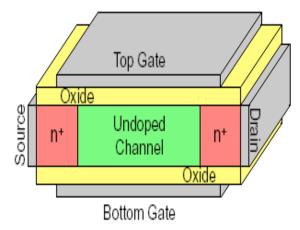

| Fig.1.17 | Schematic representation of DG MOSFET                                                                                                                                                                          | 17       |

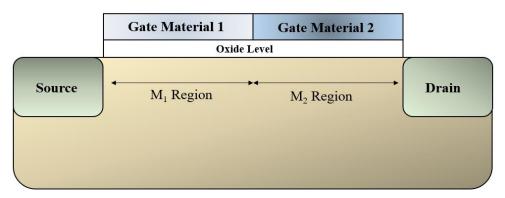

| Fig.1.18 | Schematic representation of DMG MOSFET                                                                                                                                                                         | 18       |

| Fig.1.19 | Schematic 3D structure of the asymmetrical DMDG SOI MOSFET                                                                                                                                                     | 19       |

| Fig.1.20 | Schematic 3D view of GC DMDG SOI MOSFET                                                                                                                                                                        | 21       |

| Fig.2.1  | Most promising High-k materials                                                                                                                                                                                | 39       |

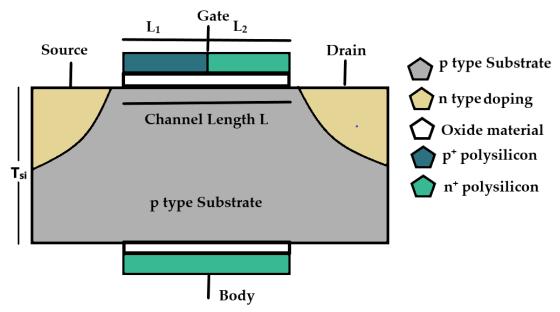

| Fig.3.1  | 2D Schematic view of the DMDG SOI MOSFET                                                                                                                                                                       | 42       |

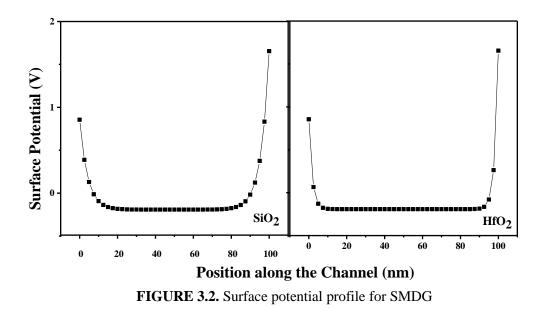

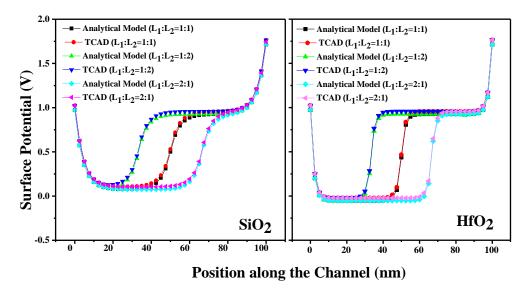

| Fig.3.2  | Surface potential profile for SMDG                                                                                                                                                                             | 57       |

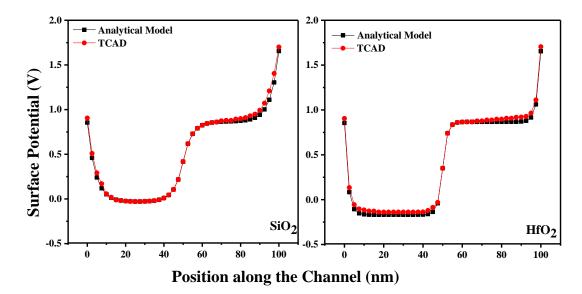

| Fig.3.3  | Surface potential profile for DMDG                                                                                                                                                                             | 58       |

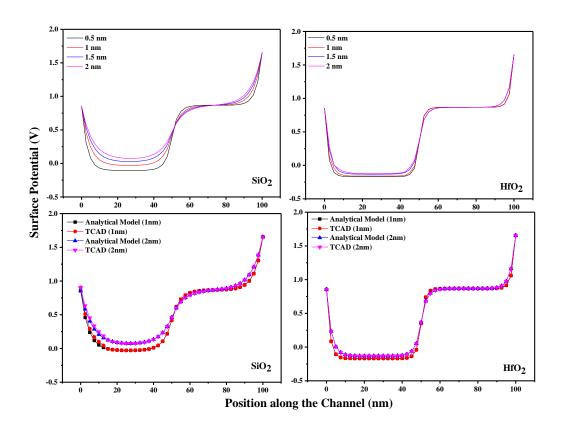

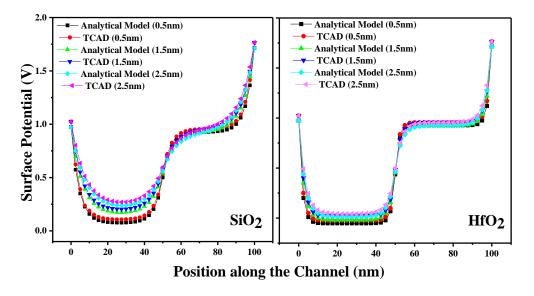

| Fig.3.4  | Change of surface potential with the channel position using different oxide thicknesses                                                                                                                        | 59       |

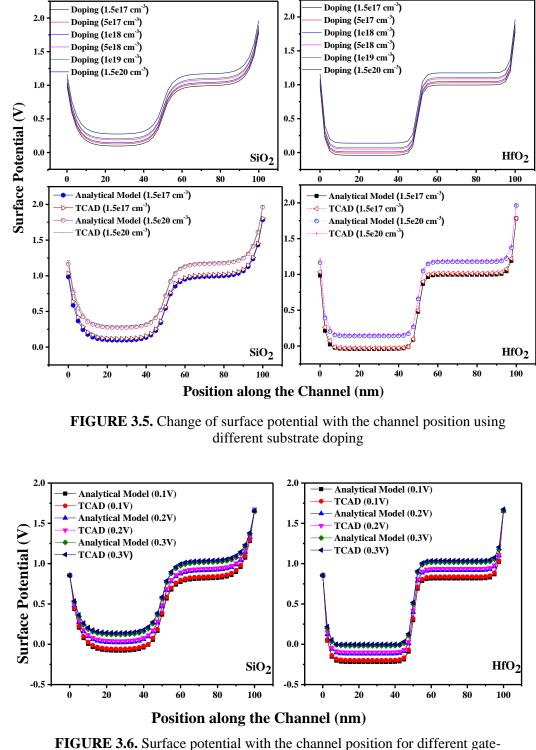

| Fig.3.5  | Change of surface potential with the channel position<br>using different Substrate Doping            | 61  |

|----------|------------------------------------------------------------------------------------------------------|-----|

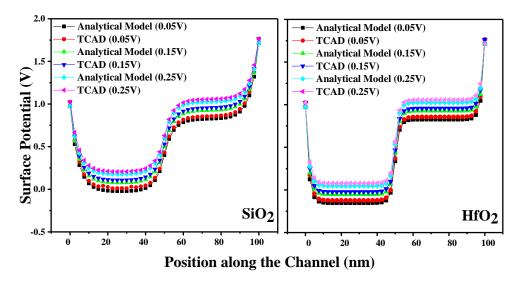

| Fig.3.6  | Surface potential with the channel position for different gate-source Voltage                        | 61  |

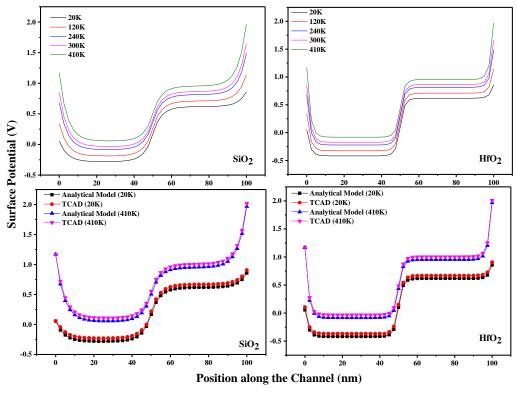

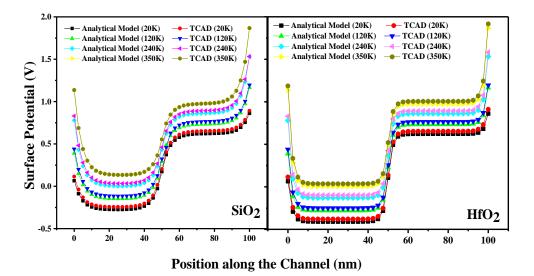

| Fig.3.7  | Change of surface potential with the channel position for different temperature                      | 62  |

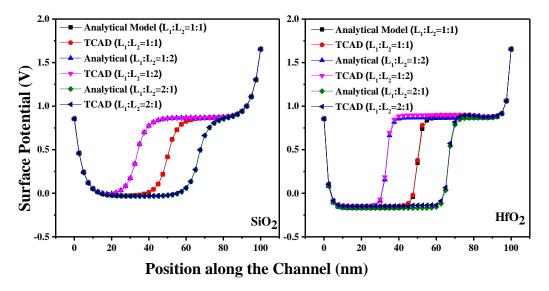

| Fig.3.8  | Surface potential with the channel position for different channel length ratio                       | 63  |

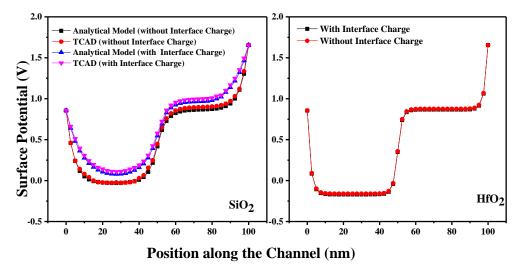

| Fig.3.9  | Surface potential with the channel position considering interface charge                             | 64  |

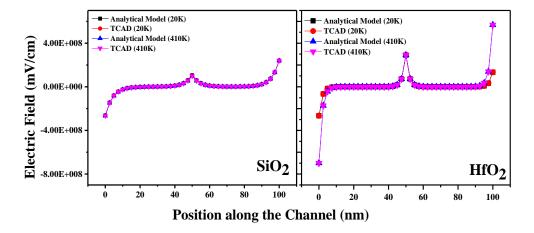

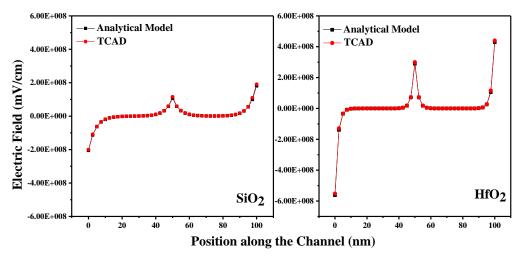

| Fig.3.10 | Comparison of electric field with channel position at different temperature                          | 65  |

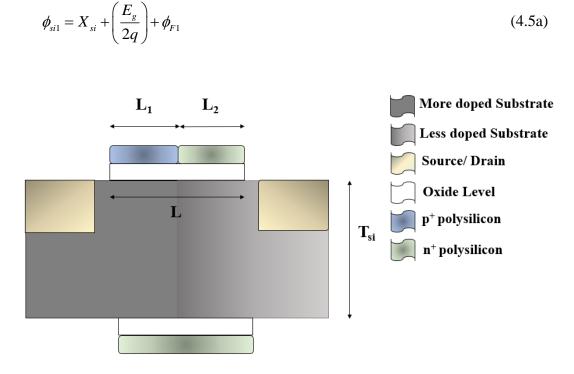

| Fig.4.1  | 2D Schematic view of the GCDMDG SOI MOSFET                                                           | 70  |

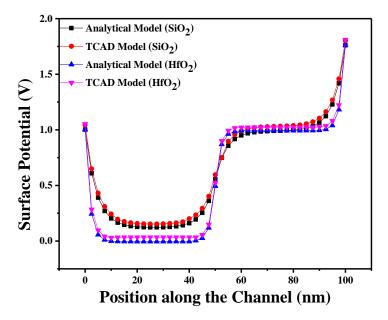

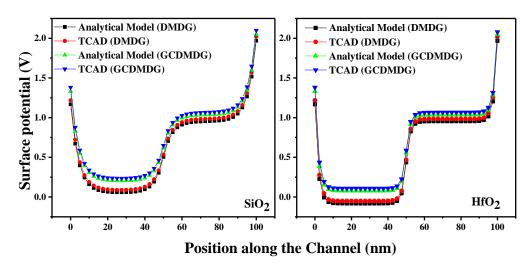

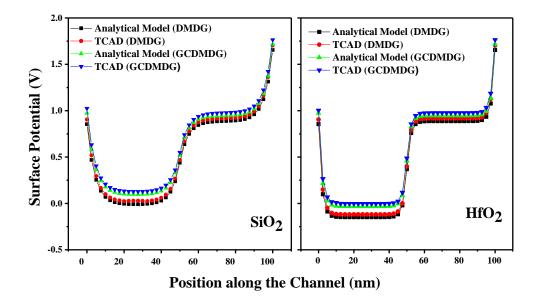

| Fig.4.2  | Change of surface potential with the channel position                                                | 83  |

| Fig.4.3  | Change of surface potential with the channel position                                                | 84  |

| Fig.4.4  | Surface potential with position along the channel for GCDMDG at different temperature                | 85  |

| Fig.4.5  | Comparison of Surface potential with position along the channel for high temperature (410K)          | 85  |

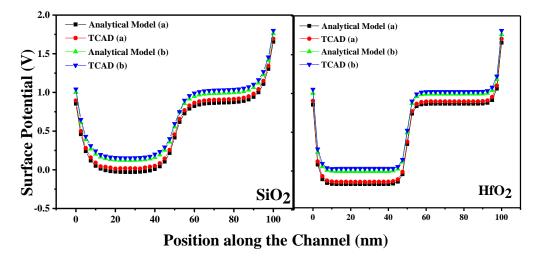

| Fig.4.6  | Development of surface potential with position of the channel for different oxide thickness          | 86  |

| Fig.4.7  | Surface potential characteristics with position along the channel for different gate source voltage  | 87  |

| Fig.4.8  | Surface potential characteristics with position along the channel for different channel length ratio | 87  |

| Fig.4.9  | Surface potential with position along the channel including interface charge                         | 88  |

| Fig.4.10 | The electric field with position along the channel for GCDMDG                                        | 89  |

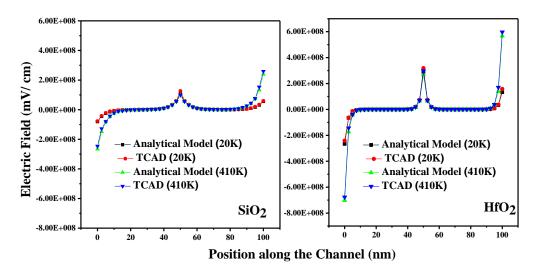

| Fig.4.11 | The electric field with position along the channel for different temperature of GCDMDG structure     | 89  |

| Fig.5.1  | 3D representation of an asymmetric SOI DMDG                                                          | 93  |

| Fig.5.2  | Representation of two double gate structures of DMDG                                                 | 94  |

| Fig.5.3  | The schematic diagram for the potential distribution of DMDG                                         | 95  |

| Fig.5.4  | 3D representation of SOI GCDMDG                                                                      | 99  |

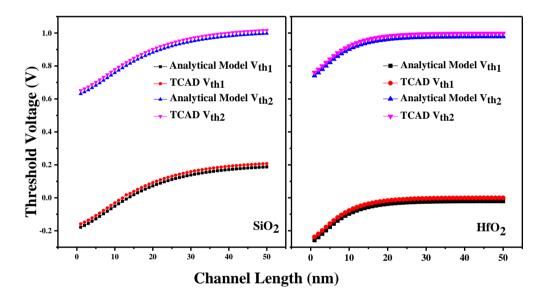

| Fig.5.5  | Threshold voltage with channel position                                                              | 104 |

|          | _                                                                                                    |     |

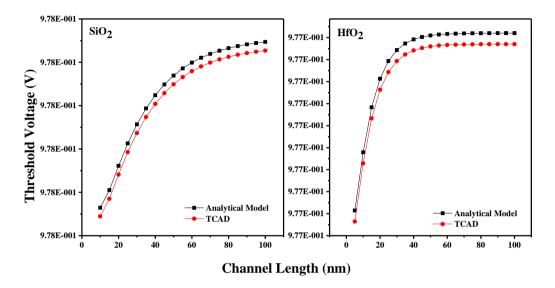

| Fig.5.6  | Threshold voltage with respect to channel length for different materials | 106 |

|----------|--------------------------------------------------------------------------|-----|

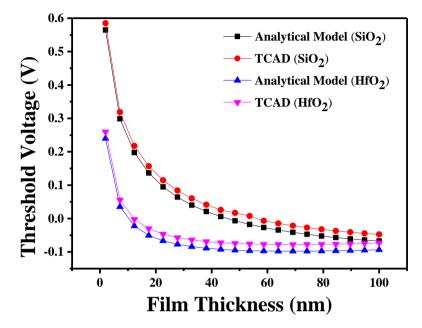

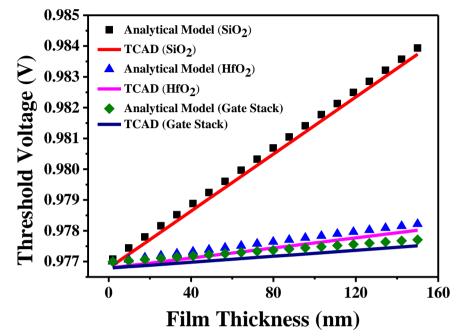

| Fig.5.7  | Threshold voltage with film thickness                                    | 107 |

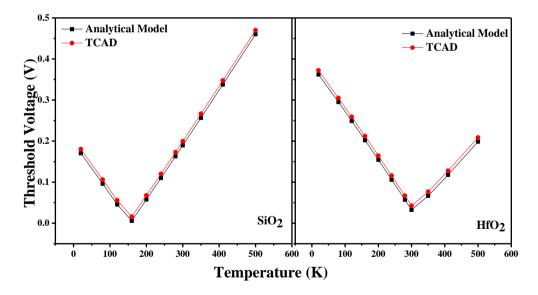

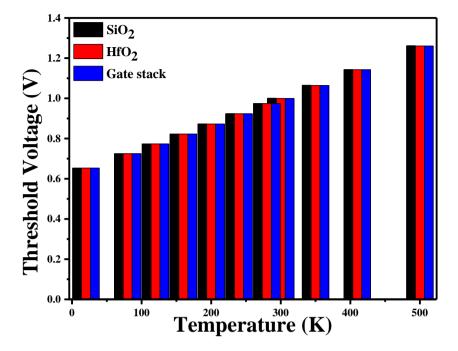

| Fig.5.8  | Threshold voltage with temperature                                       | 107 |

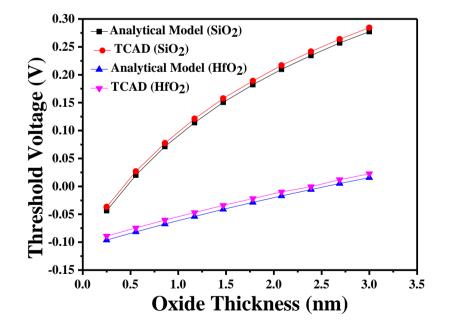

| Fig.5.9  | Threshold voltage with oxide thickness                                   | 108 |

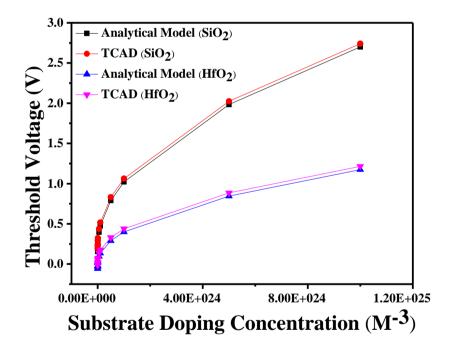

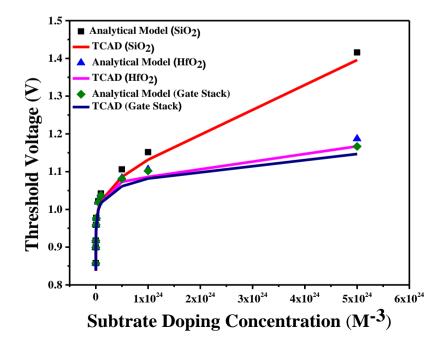

| Fig.5.10 | Comparison of threshold voltage with substrate doping concentration      | 109 |

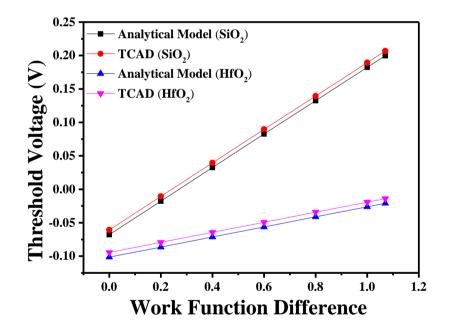

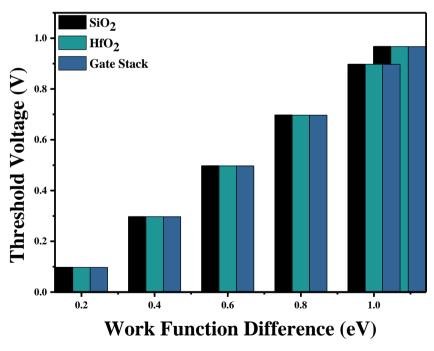

| Fig.5.11 | Relation of threshold voltage with work function difference              | 110 |

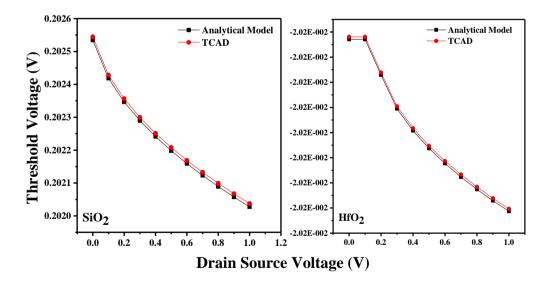

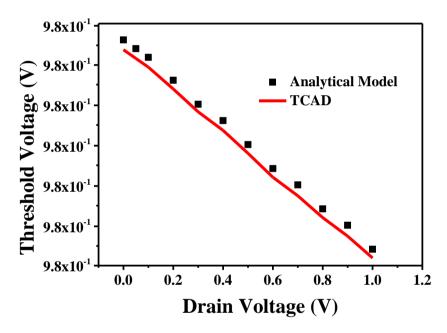

| Fig.5.12 | Threshold voltage with drain-source voltage                              | 111 |

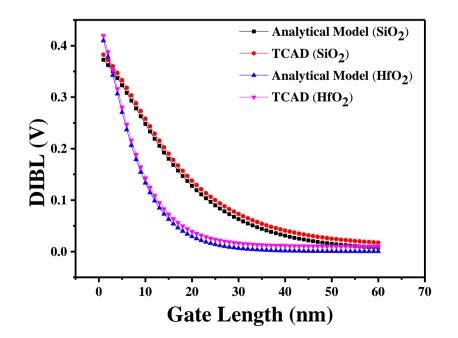

| Fig.5.13 | DIBL with channel Length                                                 | 112 |

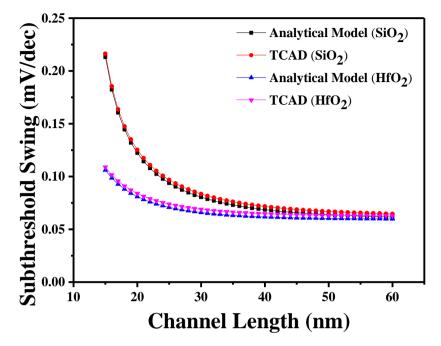

| Fig.5.14 | Subthreshold swing with channel length                                   | 113 |

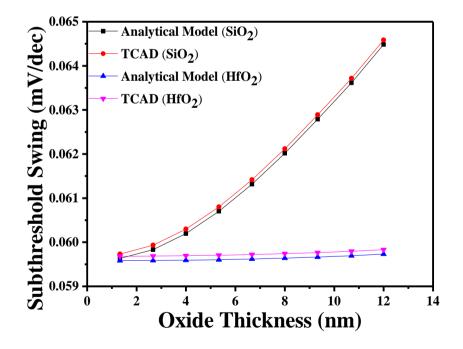

| Fig.5.15 | Subthreshold swing with oxide thickness                                  | 113 |

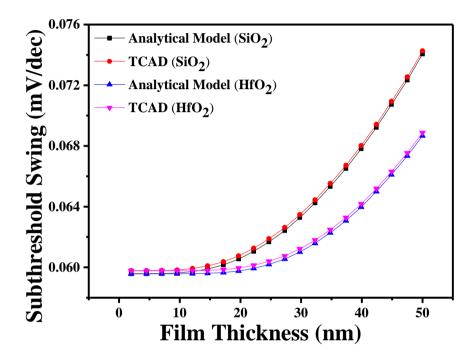

| Fig.5.16 | Subthreshold swing with film thickness                                   | 114 |

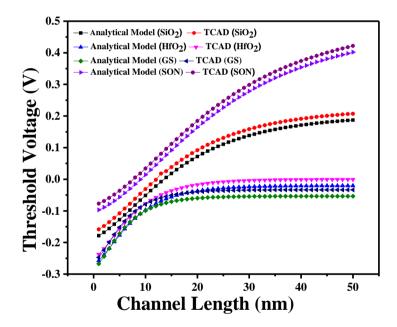

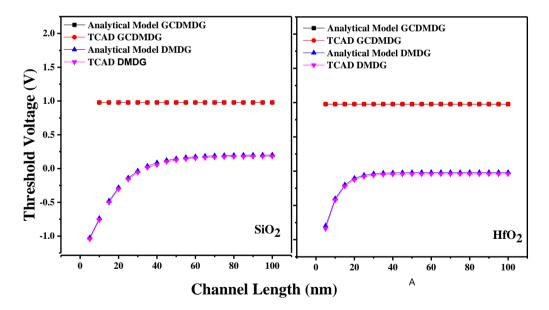

| Fig.5.17 | Threshold voltage with Channel length GCDMDG structure                   | 115 |

| Fig.5.18 | Threshold voltage for different device structure                         | 115 |

| Fig.5.19 | Threshold voltage for different doping concentration of GCDMDG           | 116 |

| Fig.5.20 | Threshold voltage for different drain voltage of GCDMDG                  | 117 |

| Fig.5.21 | Threshold voltage for different film thickness of GCDMDG                 | 118 |

| Fig.5.22 | Threshold voltage with temperature of GCDMDG                             | 120 |

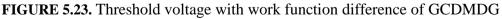

| Fig.5.23 | Threshold voltage with work function difference of GCDMDG                | 120 |

| Fig.5.24 | Threshold voltage with oxide thickness of GCDMDG                         | 121 |

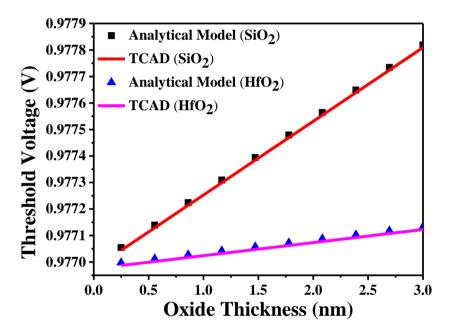

| Fig.5.25 | DIBL with channel length of GCDMDG                                       | 121 |

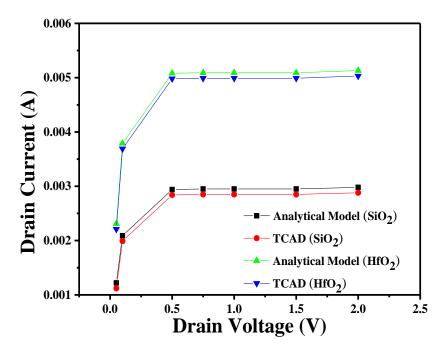

| Fig.6.1  | Drain Current with Drain Voltage                                         | 132 |

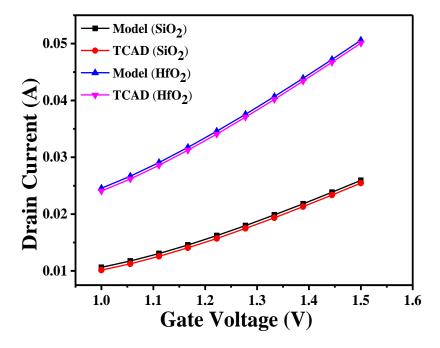

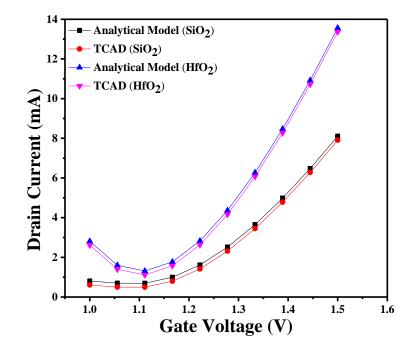

| Fig.6.2  | Drain current with gate voltage                                          | 133 |

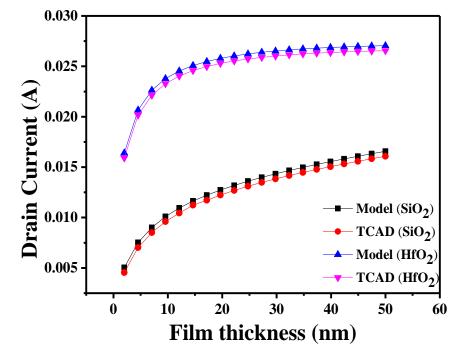

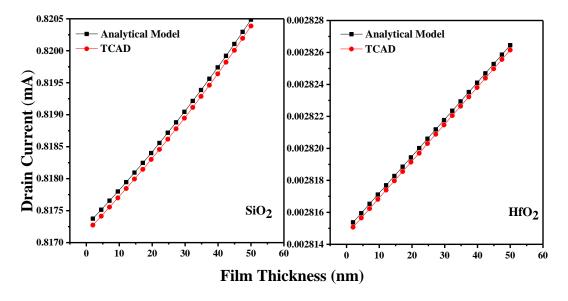

| Fig.6.3  | Drain current with film thickness                                        | 134 |

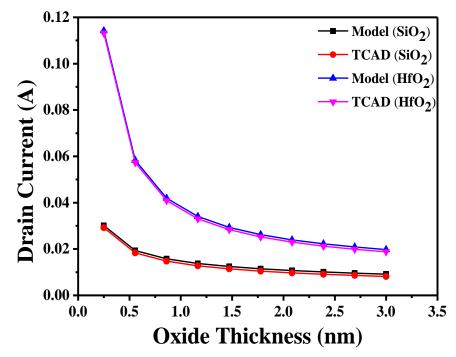

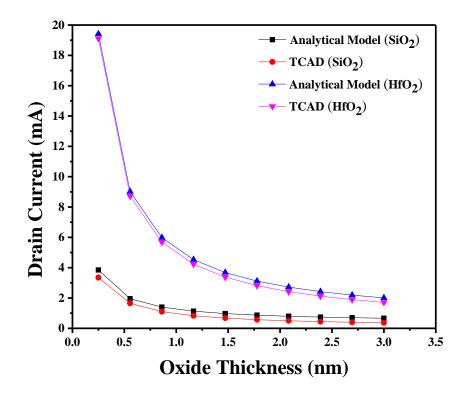

| Fig.6.4  | Drain current with oxide thickness                                       | 134 |

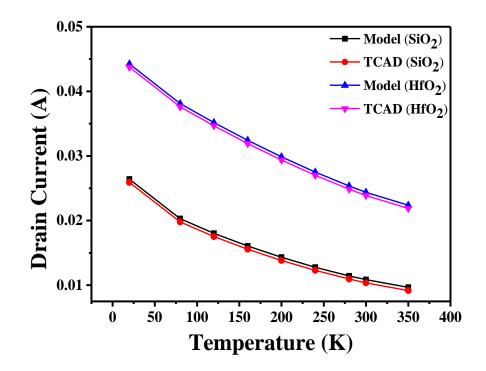

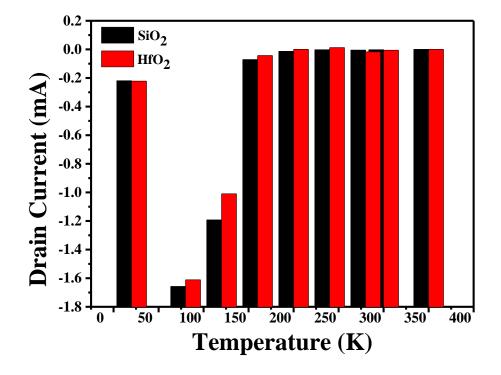

| Fig.6.5  | Drain current with temperature change                                    | 135 |

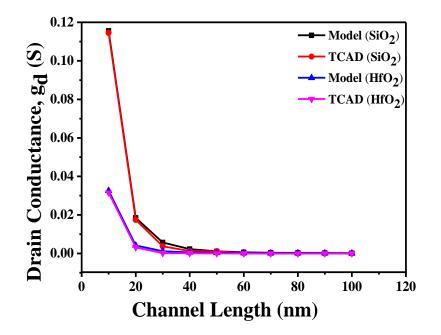

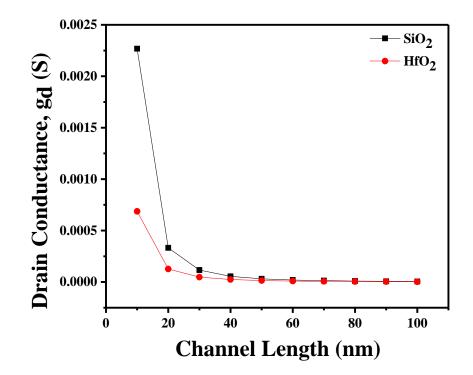

| Fig.6.6  | Drain conductance with channel length                                    | 136 |

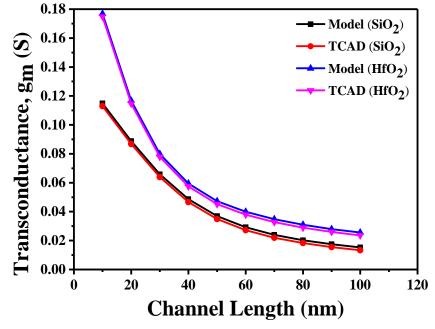

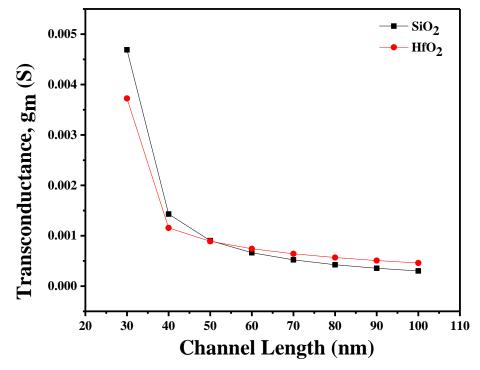

| Fig.6.7  | Transconductance with channel length                                     | 137 |

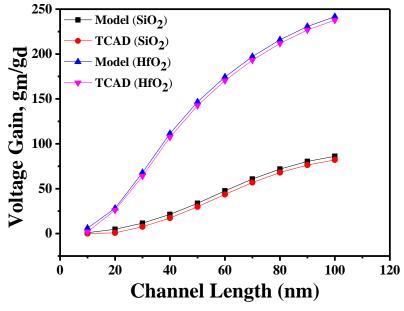

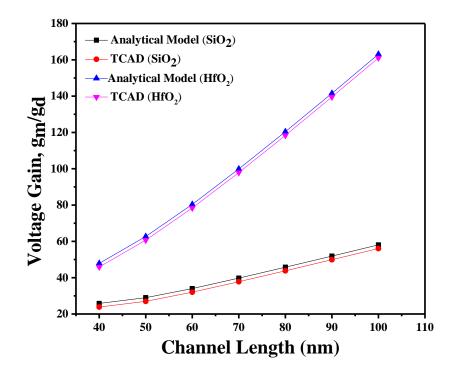

| Fig.6.8  | Voltage gain with channel length                                         | 137 |

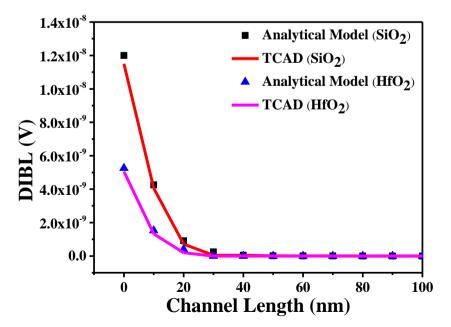

| Fig.6.9  | Drain current with drain voltage for GCDMDG                              | 138 |

| Fig.6.10 | Drain current with gate voltage for GCDMDG                               | 140 |

| Fig.6.11 | Drain current with film thickness for GCDMDG     | 141 |

|----------|--------------------------------------------------|-----|

| Fig.6.12 | Drain current with oxide thickness for GCDMDG    | 141 |

| Fig.6.13 | Drain Current with temperature for GCDMDG        | 142 |

| Fig.6.14 | Drain conductance with channel length for GCDMDG | 142 |

| Fig.6.15 | Transconductance with channel length for GCDMDG  | 143 |

| Fig.6.16 | Voltage gain with channel length for GCDMDG      | 143 |

## List of Tables

| Table No.  | Table Description                                        | Page No. |

|------------|----------------------------------------------------------|----------|

| Table 1.1. | Required dimensions for high performance over the year   | 7        |

| Table 1.2  | Design parameters                                        | 21       |

| Table 2.1  | Comparative study of all high-k materials                | 39       |

| Table 3.1  | Design parameter values for surface potential            | 56       |

| Table 4.1  | Design parameter values for GCDMDG surface potential     | 82       |

| Table 5.1  | Design parameters to evaluate threshold voltage          | 103      |

| Table 5.2  | Variation of $V_{h}$ with temperature                    | 119      |

| Table 5.3  | Variation of $V_{th}$ with work function difference      | 119      |

| Table 6.1  | Design parameters to evaluate drain current              | 131      |

| Table 7.1  | Comparative study of two devices according to parameters | 148      |

# chapter 1

# Introduction

#### 1.1 . Overview of MOSFET

"A technological innovation is like a river- its growth and development depending on its tributaries and on the conditions it encounters on its way. The tributaries to an innovation are inventions, technologies and scientific discoveries, the conditions are the vagaries of the market-place." - Ernest Braun and Stuart Macdonald (Schaller, 2004).

During World War II, the researchers realized the importance of semiconductor technology in the communication system. They also noticed the importance of silicon, germanium materials in the device structure. Around the year 1940 Teal and Gordon invented p-type and n-type semiconductors by applying impurities to the extrinsic ones. Down the path, following the vacuum tube, diode, the bipolar transistor was invented in 1947 (Fig. 1.1). After that silicon on insulator metal oxide semiconductor field effect transistor (SOI MOSFET) was first demonstrated by Mohamed Atalla and Dawon Kahng of Bell Labs in the year 1960 (Kahng, 1976). Today it has become the most important device in the integrated circuit (IC) design (Neaman). The invention of the microprocessor in the year 1971 was a milestone of this technology. Nowadays all the automation industries depend on microprocessors and microcontrollers. After inventing the complementary MOS technology the total electronic world started its journey to the very large scale integration (VLSI) era. The total evaluation path describes in Fig. 1.1.

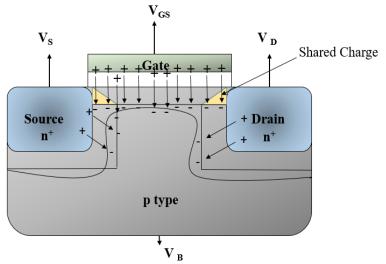

MOSFET is a planner semiconductor structure with four contacts named source (S), drain (D), gate (G) and body (B) or substrate as represented in Fig. 1.2. The doping concentration of the source and drain regions are the same and that is opposite to the

substrate region. Thus a depletion region is established between source, drain and substrate junction. Source terminal serves as the source of carriers (holes or electrons).

FIGURE 1.1. A brief chronology of the development in VLSI (Ghosh, 2013)

The drain terminal collects the carriers flown from the source through the channel. The gate terminal has total controllability over the channel formation and on the performance of the MOSFET by application of the bias. Depending on the channel formation, the MOSFET is of two types, (a) enhancement mode and (b) depletion mode. In enhancement mode, the channel is formed electrically on account of applied voltage at the gate terminal and in depletion mode, the channel is formed physically by manufacturing a physical layer between the source and drain (Tsividis, 1987). In the case of enhancement type MOSFET when the gate voltage reaches up to threshold voltage, the minority carriers are accumulated below the oxide region. Thus forming a conducting medium called a channel.

FIGURE 1.2. Cross-sectional view of a 4 terminals planar MOSFET (Tsividis, 1987)

This phenomenon is called inversion. Depending on the gate biasing, the channel transfer from the weak inversion mode to strong inversion. Also, the concentration of the minority carriers increases at the channel region during this period. Hereafter, on the application of drain-source biasing, the minority carriers move and start conducting, called drain current. Before reaching the threshold voltage channel is not formed and the current does not conduct. At this time the MOSFET is in 'OFF' state and the mode is called subthreshold. When the current starts to flow, at that time the MOSFET is in 'ON' condition (Streetman & Banerjee, 2006). A cross-sectional view of MOSFET has been represented in Fig. 1.2 with its four terminals. It has a p type substrate with n type doped source and drain. Due to p-n junction, a depletion region has been formed. On application of reverse bias voltage at the gate terminal, minority carriers are accumulated below the oxide level and formed a channel like formation. Through this channel drain current flows from drain to source on account of proper source-drain bias.

In the present technology, the MOSFET is the chief factor of advancement because of several advantages over others. Simple applications, planar structure easy to fabricate, less power consumption, high packing density, immunity to short channel effects (SCEs) and high switching speed are few among them. The high switching capability from off to on state and the proficiency during the low voltage operation make it a unique device.

#### **1.2. Sketch on MOSFET- Scaling**

In the year 1965, researcher and co-founder of Intel Corporation, Gordon Moore stated in his research paper, "Cramming more components onto integrated circuits" (Moore, 1998) that the number of transistors per chip would become double every year and that trend will continue for at least next ten years. Later on, in 1975 he slightly modified his statement and predicted that the component count per chip will be double twice the year (Moore, 2006). The prediction is illustrated as graphical representations in Fig. 1.3. It illustrated the number of components required for integrated function in log form with respect to the year. The representation clearly shows that while it required 1 or 2 components in 1960 it went up to 16 components in only 15 years. Initially, this prediction was based on 50-60 component chips and thought that this will

continue up to 1980 (Faggin et al., 1996; Moore, 1975). But this trend line continues till now in the semiconductor industry and it is so popular to gain the status of a "LAW".

FIGURE 1.3. Moore's original 1965 Graph (Dennard, 1974)

Recent trends in the semiconductor industry according to the law have been depicted in Fig. 1.4. It shows the number of components required in the advanced microprocessor and microcontroller technology starting from 1970 to now. Later Intel executive David House modified the law a little bit. He foretold that the chip performance would double every 18 months. In 1971, the first microprocessor on IC, Intel's 4004 was fabricated. The device has 16 pins and contained 2300 transistors (Plummer, 2001; Faggin, 1996). Nowadays Intel launches a microprocessor that contains nearly 2-billion components on a chip. Consequently, the component size becomes smaller approximately in every alternative year so that they can be housed in the small space. As per Moore's law (Moore, 1975), the transistor dimension is reduced by a factor of 0.7 in each technological generation (Plummer & Griffin, 2001). Recent trends of the dimension of the channel length of transistors present in the device over the year are illustrated in Fig. 1.5. The scaling of the components to smaller dimensions generates several advantages such as improve packing density, low standby power, low operating power, high performance and high speed, etc. As a result, the cost per transistor is reduced, the device can perform a more complex function and switching time is reduced. The scaling down process is represented in Fig. 1.6. With due respect to the scaling effect, every geometrical dimension of the device like channel length, width, oxide thickness, doping concentration of substrate even applied voltage has been scaled down to a factor.

FIGURE 1.4. Recent trends in semiconductor industry according to Moore's law (Wikipedia)

FIGURE 1.5. Component size over the time period (Wikipedia)

FIGURE 1.6. Scaling down process (Buvaneswari, 2019)

For scaling down, several other structural parameters have to decrease to work properly. There are two types of scaling process namely constant voltage scaling and constant field scaling. Due to constant voltage scaling, the lateral dimensions such as channel length, width are scaled down and it is a purely geometrical process. However, several SCEs have been introduced for it. In the case of constant field scaling (Dennard et al., 1974), the vertical dimensions such as source-drain junction depth, oxide thickness, power supply voltage, etc. are scaled-down and this is not a geometrical process. In the last 50 years, the channel length declines from a few hundred micrometres to the sub 20 nm range. Effectively the device faces low threshold voltage and high off current.

#### **1.3. Limitations of Scaling Effects**

The required device dimensions for high performance MOSFET over the years are represented in Table 1.1 (Hoefflinger, 2011; Zeitzoff & Chung, 2005). International technology roadmap for semiconductor (ITRS) report on 2003 conveyed that the new advancement in the device technology requires at about 1 nm oxide thickness range. Due to scaling down of the gate oxide thickness, it fails to perform as an insulator and a huge amount of charged particles starts to move through the channel region. It boosts the motion of the current across the channel. Frequently it goes up to 1A leakage current. This is sufficient to damage the device. Moreover, this current cannot be measured with the drain current (Hoefflinger, 2011). Below 1.2 nm oxide thickness the quantum mechanical tunneling effect increases, accordingly a huge amount of gate leakage current flows through the gate region (Frank et al., 2001; Garduño et al., 2011; Orouji & Rahimian, 2012). Due to the excess tunneling current, the gate oxide material SiO<sub>2</sub> breaks down. Resultantly power loss and power dissipation increase and produces surplus heat of the device (Garduño, 2011).

| Year of Production | Technology<br>Generation | Physical Length | EOT | Inversion Layer<br>Thickness | Gate Dielectric<br>Thickness | Maximum Gate<br>Leakage Limit | Power Supply | Saturation Threshold<br>Voltage | Sub Threshold Slope<br>Adjustment Factor<br>(Full depleted DG) | Source/Drain<br>Subthreshold off-<br>state Current | Mobility<br>Enhancement Factor |

|--------------------|--------------------------|-----------------|-----|------------------------------|------------------------------|-------------------------------|--------------|---------------------------------|----------------------------------------------------------------|----------------------------------------------------|--------------------------------|

| Units              |                          | nm              | Å   | Å                            | Å                            | A/cm <sup>2</sup>             | V            | V                               |                                                                | μA/μm                                              |                                |

| 2003               |                          | 45              | 13  | 8                            | 21                           | 2.20E+02                      | 1.2          | 0.21                            | 1                                                              | 0.03                                               | 1                              |

| 2004               | hp90                     | 37              | 12  | 8                            | 20                           | 4.50E+02                      | 1.2          | 0.2                             | 1                                                              | 0.05                                               | 1.3                            |

| 2005               |                          | 32              | 11  | 7                            | 18                           | 5.20E+02                      | 1.1          | 0.2                             | 1                                                              | 0.05                                               | 1.3                            |

| 2006               |                          | 28              | 10  | 7                            | 17                           | 6.00E+02                      | 1.1          | 0.21                            | 1                                                              | 0.05                                               | 1.4                            |

| 2007               | hp65                     | 25              | 9   | 4                            | 13                           | 9.30E+02                      | 1.1          | 0.18                            | 1                                                              | 0.07                                               | 2                              |

| 2008               |                          | 22              | 8   | 4                            | 12                           | 1.10E+03                      | 1            | 0.17                            | 0.8                                                            | 0.07                                               | 2                              |

| 2009               |                          | 20              | 8   | 4                            | 12                           | 1.20E+03                      | 1            | 0.16                            | 0.7                                                            | 0.07                                               | 2                              |

| 2010               | hp45                     | 18              | 7   | 4                            | 11                           | 1.90E+03                      | 1            | 0.15                            | 0.6                                                            | 0.1                                                | 2                              |

| 2012               |                          | 14              | 7   | 4                            | 11                           | 2.40E+03                      | 0.9          | 0.14                            | 0.5                                                            | 0.1                                                | 2                              |

| 2013               | hp32                     | 13              | 6   | 4                            | 10                           | 7.70E+03                      | 0.9          | 0.11                            | 0.5                                                            | 0.3                                                | 2                              |

| 2015               |                          | 10              | 6   | 4                            | 10                           | 1.00E+04                      | 0.8          | 0.12                            | 0.5                                                            | 0.3                                                | 2                              |

| 2016               | hp22                     | 9               | 5   | 4                            | 9                            | 1.90E+04                      | 0.8          | 0.1                             | 0.5                                                            | 0.5                                                | 2                              |

| 2018               |                          | 7               | 5   | 4                            | 9                            | 2.40E+04                      | 0.7          | 0.11                            | 0.5                                                            | 0.5                                                | 2                              |

Table 1.1. Required dimensions for high performance over the year

Boron that has been used to produce p type material, penetrates from the  $p^+$  polysilicon gate to the channel which enhances the detrimental impact of polysilicon depletion in the polysilicon gate region. The mobility of free carriers in the channel at inversion mode will not be sufficient to reach the required transistor performance (Yeo et al., 2003; Zeitzoff & Chung, 2005). With the scaling down of channel length, declining

from 45 nm in 2003 to 7 nm in 2018 (Schaller, 2004) increases the line edge roughness which has encountered a great challenge for the device performance.

#### 1.4. Short Geometry Effects due to Scaling

A semiconductor device is considered to be short when the device length is comparable with a depth of source/drain junction  $(X_j)$  and depletion layer width  $(X_{sd})$  for source depletion region and  $(X_{dd})$  for drain depletion region. The matter represents in Fig. 1.7. The effects are classified into two types (Das, 2015)

- (i) Short channel effects

- (ii) Narrow channel effects

**FIGURE 1.7.** Cross sectional view of MOSFET with depletion region (Ghosh, 2013)

#### 1.4.1. Short Channel Effects (SCEs)

When the channel length is comparable to the source-drain junction then it is called a short channel. However, different SCEs engender due to shortening the device dimensions are discussed below (Chaudhry & Kumar, 2004; Young, 1989).

#### 1.4.1.1. Threshold Voltage Roll Off

The depletion region charge in the channel is not created totally by the gate voltage. It is also controlled by the drain voltage specifically near the drain end. As a result, the depletion region charge which is created solely for gate voltage is reduced

by the application of drain voltage. Therefore, the threshold voltage is reduced. This effect is not only valid for short channel devices, it is applicable for long channels also. However, at the long channel, this effect can be ignored because here the amount of charges that have been generated for drain voltage is negligible (Das, 2015). Reduction or roll off nature of threshold is not desirable for any device, because for this small geometrically scaled devices can be reached to 'ON' condition at a very small gate voltage value. The depletion charge is monitored by gate voltage as well as drain voltage is shown as the triangular region in Fig. 1.9. It represents the influences of drain, source and gate terminals over the depletion region.

FIGURE 1.8. Cross sectional view of MOSFET with depletion charge sharing (Dhiman, 2018)

#### **1.4.1.2.** Sub threshold Swing (SS)

Before reaching the threshold voltage, at weak inversion mode, some amount of minority carriers are accumulated below the gate and formed a channel. As a result, before reaching the 'ON' condition mode, a small amount of current will flow through the channel. This current is called subthreshold current because before reaching the threshold voltage it flows. This can be measured analytically by the slope of the log of drain current with gate voltage (Tosaka et al., 1994),

$$S = \frac{dV_{GS}}{d(\log I_D)} \tag{1.1}$$

Here, S represents SS,  $V_{GS}$  is the gate to source voltage and  $I_D$  is the drain current.

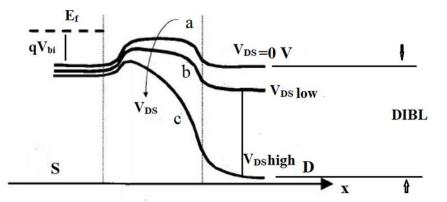

#### 1.4.1.3. Drain Induced Barrier Lowering (DIBL)

At small geometry conditions, the source and the drain regions come close together and their depletion regions approach each other. Consequently potential barrier decreases, electrons easily cross the potential barrier and carrier concentration in the channel increases. In this situation, if the drain voltage increases the drain field penetrates to the source and further decreases the barrier. This phenomenon is called 'DIBL' (Lee et al., 2010). The variation of conduction energy band edge changes its position with drain-source voltage  $V_{DS}$  is represented in Fig. 1.9. (Tsividis, 1987). At equilibrium condition, when  $V_{GS}$  is equal to flat band voltage and for  $V_{DS} = 0$  V the variation of conduction band edge is represented in Fig. 1.9 (a). However, on the application of high  $V_{DS}$ , the conduction band edge decreases Fig. 1.9 (c). Lowering the band edge is the effect of  $V_{DS}$  and the difference between the two conduction bands are represented as DIBL.

**FIGURE 1.9.** Conduction energy band edge at the surface along longitudinal direction for short channel MOSFET (a)  $V_{GS}$  equal to flat band voltage and  $V_{DS}$  is 0V, (b) Strong inversion mode, (c) strong inversion with large  $V_{DS}$  (Tsividis, 1987)

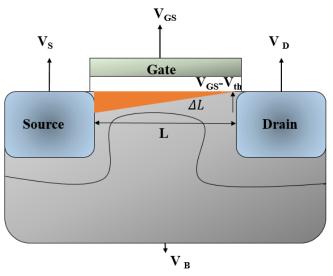

#### 1.4.1.4. Channel Length Modulation (CLM)

At the saturation region, the effective channel length ( $\Delta L$ ) of the MOSFET is decreased from the actual channel length (*L*). This is occurred due to 'pinch off' and it is a function of drain to source voltage. In long channel MOSFET, this reduction of

the channel length becomes insignificant but for small scale channel length, this reduction has to be considered. This is called CLM (Das, 2015), expressed as,

$$\Delta L = L \ln \left( 1 + \frac{\left( V_{DS} - V_{DS,sat} \right)}{V_{pp}} \right)$$

(1.2)

Here,  $V_{DS}$  is drain-source voltage,  $V_{DS,sat}$  represents saturation voltage and  $V_{pp}$  is pinch off voltage. The pinch off voltage is represented in Fig. 1.10 where the channel length touched the oxide surface and it can be represented by the difference between  $V_{GS}$  and threshold voltage  $V_{th}$ . In small dimension devices, this effect enhances to block the channel length and reduces  $I_D$ .

FIGURE 1.10. Schematic representation of CLM (Ghosh, 2013)

#### 1.4.1.5. Velocity Saturation

The drift velocity of the carrier increases with the increasing value of the electric field. But at a very high value of the electric field, this becomes saturates. This phenomenon is called velocity saturation. In a small scale MOSFET, this velocity saturation occurs at an earlier stage than a long scale device. This will reduce the 'ON' state condition of the MOSFET.

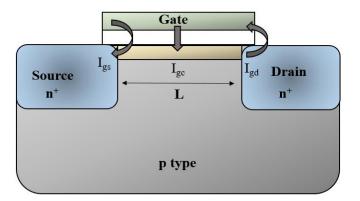

#### 1.4.1.6. Gate Oxide Leakage

Due to scaling down the MOSFET, the insulator oxide thickness goes to the 2 nm range. At this thickness level, silicon dioxide (SiO<sub>2</sub>) won't be able to perform as

good dielectric material and increases the gate tunneling current (Haensch et al., 2006). Different types of tunneling currents are represented in Fig. 1.11. The free charged particles directly penetrate the oxide level and go to the gate terminal from the source end and generate gate-source tunneling current  $(I_{gs})$ , whereas the current flow between drain and gate terminal due to movement of the charged carrier from gate to drain is called gate-drain tunneling current  $(I_{gd})$ . However, some of the carriers directly move to the channel and generate tunneling current  $(I_{gc})$ . These currents cannot contribute to drain current and damage the device. Using high-k material this problem can be overcome.

#### **1.4.2.** Narrow Channel Effects

When the channel width is comparable to depletion region thickness then the device is called a narrow channel device. The narrow channel width of the MOSFET generates some effects that are discussed below (Das, 2015).

#### 1.4.2.1. Gate Induced Drain Leakage (GIDL)

Normally, MOSFET will be at 'ON' condition after reaching the threshold voltage and that voltage is a function of gate voltage. So when the gate voltage is zero generally n-channel MOSFET will be in an 'OFF' state. However, on account of high drain voltage, the narrow width of the depletion region and band bending, a leakage current will flow. This current is known as GIDL (Tsividis, 1987). The generated electron-hole pair that have been created due to high drain voltage and causes of leakage current is depicted in Fig 1.12. Numerous electron-hole pairs are generated and they move to the substrate by penetrating the depletion region. This is the cause of the GIDL leakage current.

FIGURE 1.12. Schematic diagram of GIDL effect (Ghosh, 2013)

#### **1.4.2.2. Fringing Field Effects**

Due to the reduction of device length and width the gate region is overlapped with the source and drain. So that the electric lines have become dense at the sidewall region of the channel. These lines help to increase the concentration of free charge particles in the channel and have a great impact on the device's performance. This phenomenon is called the fringing field effect (Han & Ferry, 1998). Fig. 1.13 illustrates different fringing lines that have been generated in the case of short channel MOSFET. These lines directly affect the channel performance.

#### 1.4.2.3. Hot Carrier Effects (HCEs)

The MOSFET dimensions are scaled quite faster than the supply voltage. As a result, the horizontal and vertical parts of the electric field in the channel region increase. A higher electric field provides high kinetic energy to the free particles (hot holes and electrons). These hot carriers are injected into the gate oxide and affect the oxide interface charge distribution, current-voltage characteristics of the MOSFET. Some pictorial representation of HCEs is illustrated in Fig. 1.14 (Garrigues & Belland,

1986; Takeda, 1984). Due to high kinetic energy, several electron-hole pairs are generated and are injected into gate, drain or source terminal.

FIGURE 1.13. Cross sectional view of short channel MOSFET with fringing lines (Dhiman, 2018)

FIGURE 1.14. Cross sectional view of MOSFET with hot electrons (Ghosh, 2013)

#### 1.4.2.4. Impact Ionization

The primarily generated hot carriers collide with other atoms and generate new electron-hole pairs. This process is called impact ionization. The primary and secondary electrons both take part in the flow of drain current whereas the holes that are generated by the impact ionization flow into the substrate and generate substrate current  $(I_b)$  as in Fig. 1.15. This current is monitored by the heating effect of the device and drain electric field. The high value of substrate current increases the probability of circuit breakdown (Reddy & Kumar, 2005).

FIGURE 1.15. Cross sectional view of MOSFET showing impact ionization (Ghosh, 2013)

#### 1.4.2.5. Parasitic BJT Effect

The depletion region between source-drain and substrate generates capacitance and resistance effects. In a narrow channel, these parasitic effects become so high that they decrease the driving capability and switching speed of the device (Reddy & Kumar, 2005).

Several exclusive architectural changes have been introduced in the planar structure MOSFET to overthrow these problems. Gate engineering aspects, gate material engineering, oxide material engineering are few among them. Instead of using classical planar structure, two-dimensional or three-dimensional structures with multiple gates emerges the MOSFET technology into a new dimension. These ideas also give practical solutions to the problems. The different multiple-gates structures that have been used to fabricate the MOSFET for better performance are explained in Fig. 1.16 (Colinge et al., 1990). In this figure, several MOSFET structures with different dimensions have been shown and compare with one-dimensional planar MOSFET. Instead of using one gate, researchers use double gate structures like gate all around (GAA), multiple independent gate field effect transistor (MIGFET), double gate fin field effect transistor (FINFET) to overcome the SCEs. Among triple gate structures, trigate field effect transistor (FET),  $\Pi$  gate,  $\Omega$  gate, triple gate FINFET are renowned. These structures will provide better coverage over the channel due presence

of three gates. In the surrounding gate structure i.e cylindrical gate, quadruple gate FET covers the channel throughout all the directions. For better coverage of gate voltage, the effects of SCEs reduce.

#### 1.5. MOSFET Technology-Evaluation

Instead of using a single gate structure, many multi-gate (MuG) MOSFETs like double gate (DG), trigate (TG) and surrounding gate (SG) structures are proposed as an alternative structure over bulk MOSFET (Colinge, 2004). The double gate (DG) structure is the simplest of all MuGs. In 1967, Farrah and Steinberg of Bendix Corporation first proposed the concept of the double-gate transistor followed by Sekigawa of ETL the concept of DG MOSFET in 1980 (Farrah & Steinberg, 1967). In this structure, the channel gets covered from top to bottom by the gates. The presence of two gates gives better coverage over the small channel. On application of gate voltage from both sides of the device, the channel changes to inverting mode easily. With the better coverage of gate voltage over the channel, the uncontrolled leakage current flow is reduced. Thus this planar structure helps to reduce SCEs, improves punch through properties and also reduces the capacitance generated at the junctions (Nakagawa et al., 2003). The schematic view of DG MOSFET is represented Fig. 1.17. Two gates are represented by a grey colour on the top and at the bottom of the device. They are also called the top gate and bottom gate. Below the gates oxide layer has been fabricated showing by yellow colour representation.

In view of gate material engineering, dual material gate (DMG) architecture is another unique model used to diminish the problems of SCEs (Kumar & Chaudhry, 2004). Fig. 1.18 represents the schematic view of DMG. In this architecture, the gates are made up of two different materials with non-identical work functions such as polysilicon. In the preferred structure, the gate near the source side is used high work functioned p<sup>+</sup> polysilicon material and low work functioned n<sup>+</sup> polysilicon material is used at the gate near the drain side. Due to the dissimilarity of work function materials assembling at the gate junction, a voltage drop has been introduced. As a result, two different lobes with different values are generated at the surface potential. The generated potential profile of the surface region is modified to increase the efficiency of electron transport. The lower surface potential is generated under high work

functioned gate material and a higher one is generated under low work functioned polysilicon material.

FIGURE 1.16. Possible devices with multi-gate structure (Buvaneswari, 2019)

Figure 1.17. Schematic representation of DG MOSFET (Ghosh, 2013)

Consequently, a step function like formation has been generated. The generated threshold voltage has a low value under the first gate (near the source end) than under the second gate (near the drain end). This feature helps to increase the transportation

effectiveness of the gate. At the gate junction, the surface potential, as well as the electric field, are also adjusted according to the manner. The average lifetime of the DMG device is increased by the increment of the electric field under the gate terminal. However, due to using different work functions polysilicon materials, the step like function has been generated in the surface potential and electric field. The presence of two different lobes helps to reduce the SCEs (Kumar & Chaudhry, 2004; Saxena et al., 2002).

A unique planar model naming dual material double gate silicon on insulator (DMDG SOI) MOSFET structure is engendered in combination with these two structures. This architecture integrates the advantages of two different structures stated above.

Figure 1.18. Schematic representation of DMG MOSFET (Ghosh, 2013)

## 1.5.1. Concept and Operation of Dual Material Double Gate SOI MOSFET

DMDG SOI MOSFET structure is superior to the common planar MOSFET structure. It is formed by merging the DG and DMG concepts. It has two gates at the top and the bottom, whereas the gates consist of two different polysilicon materials of different work functions. Subsequently, the drain conductance, as well as the SCEs and DIBL reduces and the drain potential variation increases due to the presence of step function characteristics in the surface potential and electric field over the channel region. Reduction of the highest value of the electric field than other devices helps to generate uniformly extended drift velocity of the free carrier along the channel, decreases the hot carrier effects and improves drain breakdown voltages. It has a higher transconductance value which helps to reduce SCEs and enhances the voltage gain. DMDG SOI MOSFET structure with all these physical aspects upgrades itself as a major topic to the research candidates for future technology (Reddy et al., 2005; Goel et al., 2016; Kaur et al., 2008).

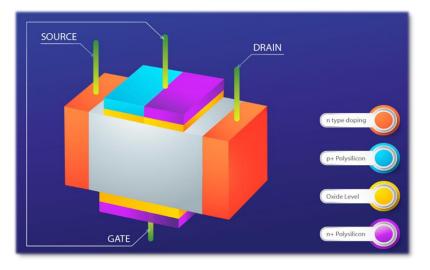

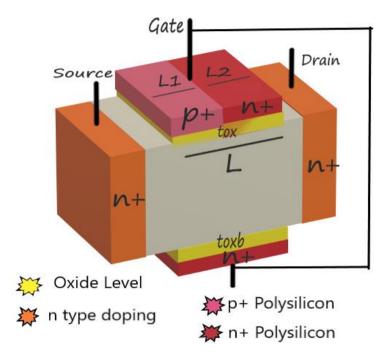

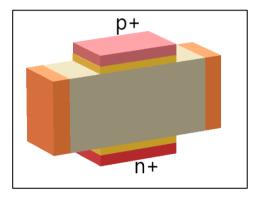

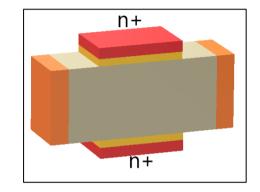

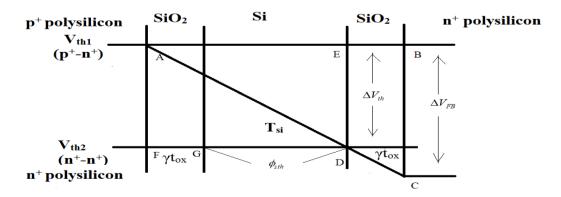

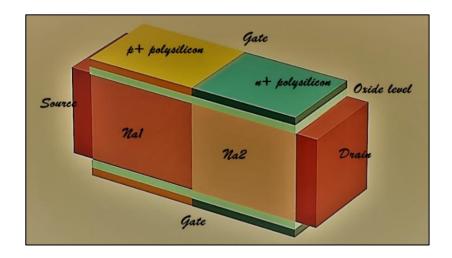

Schematic representation of fully depleted DMDG structure has been shown in Fig. 1.19. In this research work, different physical attributes like surface potential, electric field, threshold voltage and drain current are analysed of this structure. It has two gates at the top and bottom, where the top gate contains two different materials  $p^+$ polysilicon and n<sup>+</sup> polysilicon. However, the bottom gate consists of only one material  $(n^+$  polysilicon). An oxide material present between gate and substrate to serve the dielectric medium. The thickness of the oxide material for top and bottom gates are same. The total channel length is divided into two equal parts so that the particular effects of different gate materials can be studied. Simultaneously, silicon dioxide (SiO<sub>2</sub>) and high-k materials are used as gate oxides for the comparative analysis. It has two different values of surface potential and electric field for two different region. Two different types of threshold voltages are also generated due to presence of two surface potentials. However, using high-k material, it generate low value of surface potential. The slope of the surface potential near the drain side increases with high-k. This also helps to decrease the SCEs. Details analytical features and its characteristics are studied in this research work.

## 1.5.2. Concept and Operation of Graded Channel Dual Material Double Gate SOI MOSFET

The graded channel DMDG (GCDMDG) design is another modified MOSFET structure with an asymmetrically doped channel. In this structure, the doping concentration of the substrate is not uniform. It is greater on the source side than the drain side. Because of the "Doping engineering" concept, this type of structure is more feasible to fabricate than uniformly doped DMDG structure (Goel et al., 2016). Due to this type of doping nature the graded channel structure provides very good susceptibility against the SCEs, helps to improve the hot carrier movements of the device and reduces the impact ionization. Excluding all these superiorities, the GC design also generates a larger pilot current and increases transconductance in contrast with other uniformly doped devices.

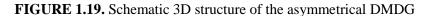

An illustrative presentation of GC DMDG SOI MOSFET is portrayed in Fig. 1.20. The diagram describes that at the front gate terminal,  $M_1$  side of the gate which locates nearer to the source is made of p<sup>+</sup> polysilicon and  $M_2$  side of the gate which locates nearer to the drain, is made of n<sup>+</sup> polysilicon. The length of the gates are  $L_1$  and  $L_2$  by agreement, whereas the gate at the backside is constructed with n<sup>+</sup> polysilicon only (Reddy et al., 2005; Khan et al., 2008; Vadthiya et al., 2018). The constant parameters that have been used to construct the DMDG and GCDMDG device model for surface potential, electric field, threshold voltage and drain current have been given in Table 1.2. These parameters with respective values have been used throughout this research work.

To overcome the quantum mechanical tunneling effects, gate oxide leakage current, etc. that have been generated due to scaling down the oxide thickness, some oxide materials with higher k values have been used instead of SiO<sub>2</sub>. It can be seen that due to some unique features they provides better result in MOSFET performance than SiO<sub>2</sub>.

FIGURE 1.20 Schematic 3D view of GC DMDG SOI MOSFET

| Sl. No. | Parameters                                                | Values                                                              |

|---------|-----------------------------------------------------------|---------------------------------------------------------------------|

| 1.      | $\mathcal{E}_{si}$ - Dielectric constant of Si            | 11.7                                                                |

| 2.      | $\mathcal{E}_{ox}$ - Permittivity of oxide                | 3.9 (SiO <sub>2</sub> ), 22 (HfO <sub>2</sub> )                     |

| 3.      | $\phi_{M1}$ - Work function of p <sup>+</sup> polysilicon | 5.25 eV                                                             |

| 4.      | $\phi_{M2}$ - Work function of n <sup>+</sup> polysilicon | 4.17 eV                                                             |

| 5.      | $E_g$ - Silicon bandgap at 300K                           | 1.14 eV                                                             |

| 6.      | $X_{si}$ - Electron affinity of Silicon                   | 4.05 eV                                                             |

| 7.      | q - Electronic charge                                     | 1.6×10 <sup>-19</sup> C                                             |

| 8.      | K - Boltzmann's constant                                  | $1.38 \times 10^{-23} \text{ m}^2 \text{ kg s}^{-2} \text{ K}^{-1}$ |

| 9.      | T - Absolute temperature                                  | 300K                                                                |

| 10.     | $C_{air}$ - Permittivity of Air                           | 1                                                                   |

#### Table 1.2. Design parameters

#### 1.6. High-k materials - Its Advantages

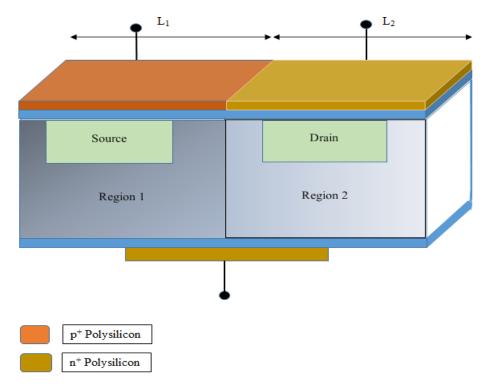

The term "High-k dielectric" refers to the material, which has a higher relative dielectric value (k) compared to the SiO<sub>2</sub> (k=3.9). The k defines the capability of the material to store energy/charge. A higher k value means a greater capacitance at a greater thickness. The uses of conventional SiO<sub>2</sub> based device reaches to physical limitation when the oxide thickness becomes a few atomic layers thick. These scaling limitations encouraged the researchers for an extensive investigation to find out new material instead of SiO<sub>2</sub> to serve as a gate oxide. When the oxide thickness becomes below 15 Å the gate leakage current exceeds about 1 A/cm<sup>2</sup> (Ribes et al., 2005). Though the usage of the high-k dielectric materials (i.e. HfO<sub>2</sub>, ZrO<sub>2</sub>, Ta<sub>2</sub>O<sub>5</sub>) as gate oxide decreases the tunnelling current and leakage power drastically however they provide amazing performance and greater energy effectiveness (Maity et al., 2016). The equivalent capacitance value of the gate parallel plate capacitor can be calculated as (Electronic Article; Choi et al., 2011),

$$C = \frac{k\varepsilon_o A}{t_{ox}}$$

(1.3)

Here, k represents the dielectric constant of the oxide,  $\varepsilon_o$  is the permittivity, A is the area of the plate and  $t_{ox}$  refers to the thickness of the oxide layer, respectively. Since the value of k is higher so it requires more thickness to obtain the same capacitive value. Qualitatively this material provides a physically thicker layer to suppress the quantum mechanical tunnelling current.

A promising high-k material should have a dielectric constant value of 10 to 30, bandgap value above 5 eV and band offset with a semiconductor substrate above 1 eV to minimize the carrier injection. A good high-k material should be thermally stable with the silicon substrate and its required thermal budget value should be below 1000 K and 90 s. The dielectric materials are mainly formed by the elements having higher atomic numbers and make ionic bonding with oxygen. At the high frequency range, the dielectric materials generate electronic polarization. So, the transition metal oxides (especially heavy metals) produce a promising high-k substance. As mentioned in (Choi et al., 2011) the properties of SrTiO<sub>3</sub> (k = 200; bandgap E<sub>g</sub> = 3 eV; electrical breakdown field,  $E_{bd} = 2.2-2.3$ ) are the most favourable for high-k material but

incompatible with MOSFET. Therefore, a perfect balance has to be considered between all the parameters to optimize the circuit performance. Remembering all these practical aspects, hafnium, zirconium and aluminium-based oxides are the best suitable with MOSFET device structure for the circuit operation as the gate leakage current is reduced by 2-3 times.

#### 1.6.1. Hafnium Dioxide and Gate Stack Concept

In this research work, hafnium dioxide HfO<sub>2</sub> (k=22) has been used as a high-k dielectric material. HfO<sub>2</sub> has some unique advantages over the other high-k materials that assist to enhance the device performance. The high dielectric constant combines with comparatively larger bandgap (5.7 eV), larger heat of formation (271 kcal/mol,), good thermal and chemical stability on silicon and larger barrier heights at the interface with Si. Despite so many advantages, high-k oxide material cannot be used directly on the Si substrate interface. It will create a large amount of interface charge due to a fabrication problem. Also, Si-SiO<sub>2</sub> bonding is much better than any other substrate-oxide bonding. To overcome this problem the gate stack concept has been introduced. A thin layer of SiO<sub>2</sub> has been incorporated on the Si surface then high-k oxide material has deposited. This architecture helps to overcome the generation of unwanted interface charge density. The oxide thickness can be calculated by combining the oxide thickness of the duo and called the effective oxide thickness (EOT) (Kaur et al., 2008; Maity et al., 2017). It can be calculated as,

$$t_{oxeff} = t_{si} + \left\{ \left( \frac{\varepsilon_{si}}{\varepsilon_{highk}} \right) \times t_{highk} \right\}$$

(1.4)

Here,  $t_{oxeff}$  represents the effective oxide thickness,  $t_{si}$  and  $t_{highk}$  are the thickness of silicon dioxide and high k material layer respectively,  $\varepsilon_{si}$  and  $\varepsilon_{highk}$  are the dielectric constant of SiO<sub>2</sub> and high-k material respectively. Normally, the thickness of the SiO<sub>2</sub> and HfO<sub>2</sub> layers are being considered as 1nm (Maity & Maity, 2020; Maity et al., 2017).

## 1.7. Scope of Study

The DMDG SOI MOSFET structure is the most basic MuG MOSFET structure, and it outperforms other planar MOSFET structures. This structure incorporates the best features of both the DG and DMG structures. Because it has a larger transconductance and a lower drain conductance value, so it may reduce all forms of SCEs and improves drain breakdown voltages (Goel et al., 2016; Reddy & Kumar, 2005). As a result, it will be easier to create the model for removing SCEs using the DMDG structure. The GCDMDG structure has several advantages over the uniform structure because of the varied doping concentrations (Noor et al., 2016; Kaur et al., 2008; Vadthiya et al., 2018). Furthermore, a graded doping concentration channel is practically implementable. It may be more capable of reducing SCEs in terms of threshold voltage roll off, providing improved surface potential, and lowering the electric field's peak value.

According to many review studies, the surface potential and electric field characteristics of the DMDG structure and GCDMDG exhibit good similarities of simulated data with analytical data. When compared to the analytical and matching simulating model, these structures are predicted to deliver a wide variety of benefits as well as many parts of the research. The generated step function-like characteristics in the surface potential and electric field over the channel (smaller in the higher work function region than the lower work function region (Reddy & Kumar, 2005) can be predicted to increase the drain potential variation and drain conductance while reducing SCEs and DIBL. As the highest value of the electric field distribution helps to generate uniformly expanded drift velocity of the electron along the channel so it will help to minimize the HCEs which is a major problem of general MOSFET. The step potential will increase with the influence of temperature, interface charge effect, etc. However, instead of utilising a uniform channel length ratio for different gate materials, it is expected that if it is increased, improved performance can be produced.

Two threshold voltages have been generated for DMDG and GCDMDG structures due to differing gate materials (Goel et al., 2016). Two threshold voltages may provide improved leakage current coverage. It is the most important aspect of a device performance. Because of the small scale dimension, it is expected that the

threshold voltage in the DMDG and GCDMDG structures will remain nearly the same up to 20 nm channel length and provide the lowest roll off factor. The generated threshold voltage may be less than 1V to improve switching characteristics. The DMDG device will have the ability to consume low power while also potentially lowering the power dissipation factor. The GCDMDG structure may also be more resistant to SCEs than a uniform doping DMDG structure. Both types of DMDG structure will provide excellent performance over the current characteristics. It will increase the voltage gain property in terms of transconductance and drain conductance. The structure is expected to give improved on current and off current features. DMDG might be a better option for removing DIBL and SS. As per the report, the uniform doping DMDG structure will provide a better switching capability.

HfO<sub>2</sub>, a high-k material, can improve all of the above features (Ribes et al., 2005; Maity et al., 2016). It is anticipated that it will improve immunity to SCEs. The highk features that are developed may provide better outcomes than typical SiO<sub>2</sub>.

Despite all the benefits, the DMDG structure has a major disadvantage due to its asymmetric structure. It is having some structural issues incorporating contemporary MOS technology. But with the change in few steps in the device fabrication process researchers may be overcome the problem. This work will enhance the prospect of fabricating a DMDG MOSFET with high-k to achieve the respective advantages which it promises.

### 1.8. Thesis Organisation

The Thesis is organized as follows

Chapter 2 states the detailing of literature review of different MUG MOSFETs structures with the application of gate material engineering. DG and DMG structures are elaborately discussed here. Various doping engineering aspects, i.e use of uniformly doping nature and graded doping nature over DMDG structure are also documented. Detail discussions on the performance exploration also have been depicted based on different architectures. Vast usage of the high-k materials and the most promising high-k, which is compatible with MOSFET is also being documented.

Chapter 3 describes the analytical modeling part of surface potential and electric field of DMDG structure using  $SiO_2$  as an oxide interface. The modeling structure

depends on the two-dimensional Poisson's equation and some boundary conditions. All these things are clearly described in this chapter. The surface potential and electric field characteristics of the device depend on some external parameters like temperature, oxide thickness, gate-source voltage, interface charge, etc. All these parameters are incorporated in the modeling and try to investigate the variation of performance. This chapter also describes the detailed comparison of the influence of high-k material over the device characteristics and compares it with conventional SiO<sub>2</sub>. All the characteristics of surface potential and electric field that have been generated from the analytical model are also compared with the simulation result.

Chapter 4 derives the surface potential and electric field modeling of GCDMDG MOSFET structure simultaneously. This model also can be derived with the help of two-dimensional Poisson's equation and boundary conditions. The influence of several parameters over the characteristics is illustrated here. Like the earlier one, these characteristics also try to compare using the high-k material as the oxide interface. All results are confirmed with respective simulation results.

Chapter 5 elaborates the threshold voltage of DMDG and GCDMDG structure. The analytical model of the threshold voltage can be derived with the help of surface potential. The analytical model of subthreshold swing and DIBL is incorporated in the threshold voltage model and discusses the performances over the SCEs. In this chapter, the impact of different parameters over the model, like reduction of channel length and film thickness, temperature effects, etc. have been derived. Using HfO<sub>2</sub> on the threshold voltage model relates the performances over SiO<sub>2</sub> on the ground of SCEs. All the characteristics that have been generated are also confronted with the simulation result.

Chapter 6 also simultaneously represents the detailing of drain current of DMDG and GCDMDG structure and tries to relate the performances concerning amplification factor. The variation of transconductance, drain conductance and voltage gain over the channel length for different devices have been compared over the SCEs and performance ground. Here also, the influence of different parameters have derived over the basic model. At last, all the derived representations are related to the simulation results. At the end of the thesis, in chapter 7 the total research work has been concluded. The total research work mainly deals with two different types of devices DMDG and GDMDG with high-k material. In this chapter, the conclusion has been derived based on the capability of swapping the SCEs keeping in mind the performance analysis using high-k. Some future aspects of this work are also being discussed in short.

# **CHAPTER**

# **DMDG MOSFET-A Review**

### 2.1. Overview of Semiconductor Technology

In 1926 scientist Julius Edgar Lilienfeld first demonstrated semiconductor-based technology in his patent "Method and Apparatus for Controlling Electric Currents" (Lilienfeld, 1926). He first introduced a field-effect transistor (FET) with three electrodes made of copper sulfide. But he was unable to fabricate the device. In the year 1940, the p-n junction diode was discovered by Russell Shoemaker Ohl (Ohl, 1946; Scaff & Ohl, 1947). After this William Shockley introduced a p-n junction-based transistor (Shockley, 1949; Shockley et al., 1951) in 1948. This was the milestone in the advancement of the semiconductor industry. Bell laboratory fabricated the transistor successfully in 1951 (Shockley et al., 1951). Sooner it became very essential in the circuit design sector because of its rectification and amplification property. IC was demonstrated by scientist Jack Kilby of Texas Instruments in 1958 (Kilby, 1976). After that, MOSFET was presented by John Atalla and Dawon Kahng of Bell Labs in 1960 (Kilby, 1976). MOSFET is a common device structure (Nicollian et al., 1982) and has become an essential device in the modern electronic world because of its switching and amplification properties. The input impedance of a MOSFET is extremely high, of the order of several Mega-Ohm (M $\Omega$ ). The circuit consumes extremely low power due to its high input impedance which helps in the generation of high-level IC and very complex performance in simpler manner. The low power consumption of MOSFET, allow the circuitry to adjust more components per chip surface area. In package form its physical dimension goes below 4 mm<sup>2</sup> (Wikipedia). Apart from that it has the ability to shorten its size while the performance remains almost same. It has a very thin active area so that the size will be in more compact form. It has no gate diode so that it can operate directly on the application of positive or negative voltage. So the device structure is used widely in the complementary MOS (CMOS) logic IC.