## MODELING, SIMULATION AND PERFORMANCE ANALYSIS OF FINFET

## A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

SUPARNA PANCHANAN

**MZU REGN NO: 1905393**

Ph. D. REGN NO: MZU/Ph.D./1682 of 24.07.2019

DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING

SCHOOL OF ENGINEERING AND TECHNOLOGY

OCTOBER, 2022

#### MODELING, SIMULATION AND PERFORMANCE ANALYSIS OF FINFET

BY

#### SUPARNA PANCHANAN

Department of Electronics & Communication Engineering

Name of Supervisor: Prof. Niladri Pratap Maity

Submitted

In partial fulfillment of the requirement of the Degree of Doctor of Philosophy in Electronics & Communication Engineering of Mizoram University, Aizawl

Department of Electronics And Communication Engineering School of Engineering and Technology MIZORAM UNIVERSITY (A Central University) Tanhril, Aizawl - 796 004, Mizoram

#### **CERTIFICATE**

This is to certify that the thesis entitled "Modeling, Simulation and Performance Analysis of FinFET" submitted to Mizoram University for the award of the degree of Doctor of Philosophy in Electronics and Communication Engineering by Suparna Panchanan, Ph.D. Registration No. MZU/Ph.D./1682 of 24.07.2019, is Ph.D. scholar in the Department of Electronics and Communication, under my guidance and supervision and has not been previously submitted for the award of any degree in any Indian or foreign University. She has fulfilled all criteria prescribed by the UGC (Minimum Standard and Procedure governing Ph.D. Regulations). She has fulfilled the mandatory publication (Publication enclosed) and completed Ph.D. course work. It is also certified that the scholar has been admitted in the Department through an entrance test, followed by an interview as per UGC Regulation of 2016.

Date: October, 2022 Place: Aizawl (Prof. NILADRI PRATAP MAITY) Supervisor

#### MIZORAM UNIVERSITY Aizawl - 796 004

#### October 2022

#### DECLARATION

I, **Suparna Panchanan**, hereby declare that the subject matter of this thesis entitled "**Modeling, Simulation and Performance Analysis of FinFET**" is the record of work done by me, that the contents of this thesis did not form basis of the award of any previous degree to me or to do the best of my knowledge to anybody else, and that the thesis has not been submitted by me for any research degree in any other University/Institute.

This is being submitted to the Mizoram University for the degree of Doctor of Philosophy in **Electronics and Communication Engineering**.

Date:

#### (SUPARNA PANCHANAN) Candidate

#### (Prof. NILADRI PRATAP MAITY) Supervisor

(Dr. RESHMI MAITY) Head of the Department Electronics and Communication Engineering

## Acknowledgement

This thesis carries the mark of several individuals. I want to start by thanking the omnipotent God for providing me the opportunity to conduct research and making it possible to complete my assignment. I would want to thank everyone who contributed to the successful completion of this dissertation. I gratefully thank my mentor, **Prof. Niladri Pratap Maity**, for his tremendous direction, inspiration, and advice throughout the progress of my research. I shall always remember his valuable suggestions for solving the glitch in my study. I would like to show my gratitude to **Dr. Reshmi Maity**, Head of the Department of Electronics and Communication Engineering, MZU for her constant encouragement and motivation. I am thankful to the entire department for their cooperation and criticisms, which lead to this work towards more perfection. I appreciate the assistance I received from **Mr. Michael Lalruatfela**, **Mr. Ch. Gopi Chand**, **Mr. Firdoos Jaman** and **Mr. Mrigankadeep Bharadwaj** throughout my entire journey.

I would like to express my deepest gratitude to **Mr. Pulak Mazumder** former HOD, **Dr. Dipankar Biswas** present HOD of the Electronics and Communication Engineering department of Regent Education and Research Foundation Group of Institutions for their administrative support. I am very grateful to **Mr. Sukdeb Saha**, **Mr. Milan Mazumdar**, **Dr. Himeli Chakrabarti**, **Mr. Jit Modak**, **Dr. Rajdeep Chakravarty**, **Dr. Anindita Das**, **Ms. Debarati Ghosh**. I want to thank the entire family of **Regent Education and Research Foundation Group of Institutions**, **Barrackpore**, **Kolkata - 700121** for giving me the support to carry forward my research work.

I would like to express my sincere appreciation to **Mr. Avik Ghosh Dastidar** and **Dr. Deepanwita Ghosh** for being with me during the entire journey. Last but not least, I would like to take advantage of this occasion to express my appreciation and gratitude to my family for their support, encouragement, and assistance throughout the voyage of my Ph.D. work.

(SUPARNA PANCHANAN)

| <br>PAGE NO. 🛛 ii 📗 |  |

|---------------------|--|

|                     |  |

# Content

#### Page No.

| Acknowledgement                                    | i  |

|----------------------------------------------------|----|

| List of Figures                                    | 6  |

| List of Tables                                     | 13 |

| Abbreviation                                       | 14 |

| Symbols                                            | 18 |

| Introduction                                       | 21 |

| 1.1. Background                                    | 21 |

| 1.2. Short Channel Effects                         | 25 |

| 1.2.1 Velocity saturation and Mobility degradation | 25 |

| 1.2.2 Drain induced barrier lowering               | 26 |

| 1.2.3 Threshold voltage roll-off                   | 27 |

| 1.2.4 Channel length modulation                    | 27 |

| 1.2.5 Punch through                                | 29 |

| 1.2.6 Hot carrier effect                           | 29 |

| 1.2.7 Impact ionisation                            | 30 |

| 1.2.8 Subthreshold swing                           | 31 |

| 1.2.9 Quantum mechanical effect                    | 31 |

PAGE NO. || 1 ||

| 1.2.10 Gate induced drain leakage               | 32 |

|-------------------------------------------------|----|

| 1.2.11 Fringing induced barrier lowering        | 32 |

| 1.2.12 Parasitic BJT effect                     | 33 |

| 1.2.13 Time-dependent dielectric breakdown      | 34 |

| 1.3 Multi-gate MOSFET                           | 34 |

| 1.4 Concept of FinFET                           | 37 |

| 1.5 Need for High-k materials                   | 38 |

| 1.5.1 Why HfO <sub>2</sub> ?                    | 41 |

| 1.6 Scope of the thesis                         | 41 |

| 1.7 Thesis organisation                         | 43 |

| <u>FinFET – A Review</u>                        | 46 |

| 2.1. Introduction                               | 46 |

| 2.2. Annals of FinFET                           | 46 |

| 2.3 Structure of FinFET                         | 47 |

| 2.4. Fabrication Challenges                     | 50 |

| 2.4.1 Fin patterning                            | 50 |

| 2.4.2. Fin shape                                | 50 |

| 2.4.3. Gate length scaling                      | 51 |

| 2.4.4. Doping                                   | 52 |

| 2.4.5. Orientation of fins                      | 53 |

| 2.4.6. Reliability                              | 53 |

| 2.4.7. Parasitic capacitance                    | 53 |

| 2.5. Review of FinFET                           | 53 |

| 2.5.1. SOI and Bulk FinFET                      | 53 |

| 2.5.2. Shorted-Gate and Independent-Gate FinFET | 57 |

| 2.5.3. Double-Gate FinFET                       | 58 |

| 2.5.4. Triple-Gate FinFET                       | 61 |

| 2.5.5. Multi-Gate FinFET                        | 62 |

| 4.4 Summary                                            | 134 |

|--------------------------------------------------------|-----|

| 4.3. Results and Discussions                           | 125 |

| 4.2.3 Threshold voltage for TG-FinFET                  | 120 |

| 4.2.2 Threshold voltage for asymmetrical FinFET        | 118 |

| 4.2.1 Threshold voltage for symmetrical FinFET         | 115 |

| 4.2. Analytical Model of Threshold Voltage             | 115 |

| 4.1. Introduction                                      | 112 |

| Threshold Voltage                                      | 112 |

| 3.4 Summary                                            | 110 |

| 3.3. Results and Discussions                           | 99  |

| 3.2.4 Electric field model for TG-FinFET               | 98  |

| 3.2.3 Surface potential model for TG-FinFET            | 96  |

| 3.2.2 Surface potential model for asymmetric DG-FinFET | 90  |

| 3.2.1 Surface potential model for symmetric DG-FinFET  | 83  |

| 3.2. Analytical Model of Surface Potential             | 83  |

| 3.1. Introduction                                      | 81  |

| Surface Potential and Electric Field                   | 81  |

| 2.6. Summary                                           | 79  |

| 2.5.13. Application of FinFET                          | 79  |

| 2.5.12. Application of germanium in FinFET             | 77  |

| 2.5.11. Fabrication of FinFET                          | 73  |

| 2.5.10. Capacitive and Resistive study of FinFET       | 70  |

| 2.5.9. FinFET with different fin shape                 | 67  |

| 2.5.8. Multiple fin FinFET                             | 67  |

| 2.5.7. Quantum FinFET                                  | 66  |

| 2.5.6. Symmetric high-k Spacer hybrid FinFET           | 65  |

PAGE NO. || 3 ||

| Drain Current                              | 136 |

|--------------------------------------------|-----|

|                                            |     |

| 5.1. Introduction                          | 136 |

| 5.2. Analytical Model for Drain Current    | 139 |

| 5.3. Results and Discussions               | 146 |

| 5.4 Summary                                | 154 |

| Trans-Capacitance                          | 156 |

| 6.1 Introduction                           | 156 |

| 6.2 Analytical Model for Trans-Capacitance | 159 |

| 6.3 Results and Discussions                | 169 |

| 6.4 Summary                                | 175 |

| Fin Shape Effect                           | 177 |

| 7.1. Introduction                          | 177 |

| 7.2. Analytical Model                      | 179 |

| 7.3. Results and Discussions               | 182 |

| 7.4 Summary                                | 190 |

| Conclusion and Future Scope                | 192 |

| 8.1. Conclusion                            | 192 |

| 8.2. Future Scope                          | 196 |

| <b>Reference and Bibliography</b>          | 197 |

| Index                                      | 209 |

| PAGE NO.    4                              |     |

PAGE NO. || 4 ||

| Content |

|---------|

|---------|

| Bio-data of the Candidate    | 213 |

|------------------------------|-----|

| List of publications         | 214 |

| Journal Publications         | 214 |

| Conference publications      | 215 |

| Particulars of the Candidate | 216 |

|--|

## **List of Figures**

#### Page No.

| Fig.1.1: Road Map for Moore's Law (Moore, 1975)2                                    | 22 |

|-------------------------------------------------------------------------------------|----|

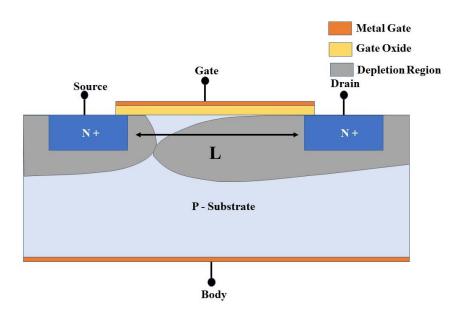

| Fig.1.2: Cross-sectional structure of MOSFET (D. Das, 2015)                         | 24 |

| Fig.1.3: Cross-sectional structure of CMOS (Chattopadhyay, 2006)                    | 24 |

| Fig.1.4: Cross-sectional view of SOI MOSFET structure (D. Das, 2015)                | 25 |

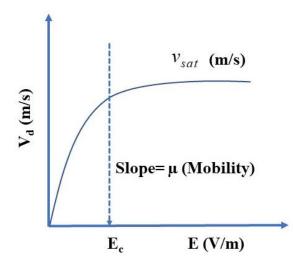

| Fig.1.5: Representing velocity saturation $(v_{sat})$ (D. Das, 2015)                | 26 |

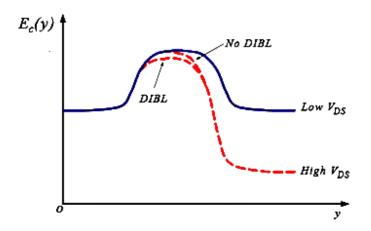

| Fig.1.6: Bending of conduction due to DIBL (Yannis Tsividis, 1987)2                 | 27 |

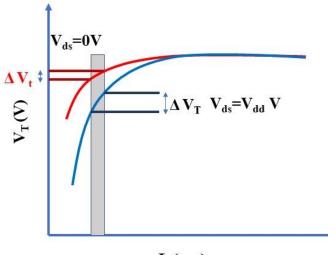

| Fig.1.7: Representing $\Delta V_T$ (Sze, Li, & Ng, 2021)                            | 28 |

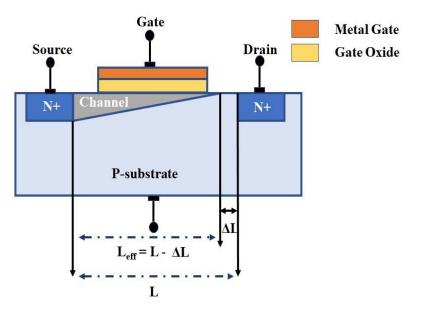

| Fig.1.8: Block diagram representing channel length modulation                       | 28 |

| Fig.1.9: Schematic diagram of punch through (Yannis Tsividis, 1987)2                | 29 |

| Fig.1.10: The hot electron effect (D'Agostino & Quercia, 2000)                      | 30 |

| Fig.1.11: Schematic representation of the impact ionisation process (Bhattacharyya, |    |

| 2009)                                                                               | 30 |

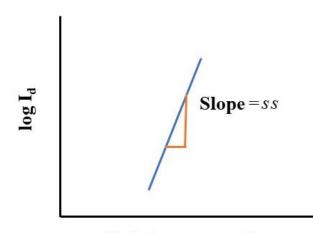

| Fig.1.12: $\log I_d$ Vs $v_{gs}$ curve (D. Das, 2015)                               | 31 |

| Fig.1.13: Graphical representation of GIDL (JH. Chen, Wong, & Wang, 2001)3          | 32 |

| Fig.1.14: Schematic representation of FIBL (Mohapatra et al., 2003)                 | 33 |

| Fig.1.15: Scaling scenario for device architecture and development of device        |    |

| architecture in the IRDS Roadmap (IEEE, 2020)                                       | 36 |

| Fig.1.16: Classification of FinFET (Lakshmi, 2013)                                  | 36 |

| Fig.1.17: Schematic view of TG-FinFET                                               | 38 |

| Fig.1.18: Band diagram showing the band offset (Persson, 2004)                      | 40 |

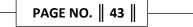

| Fig.2.1: DIBL and SS with alteration of $L_{EFF}$ for DG and bulk silicon nFET's    |    |

| (Nowak et al., 2004)4                                                               | 17 |

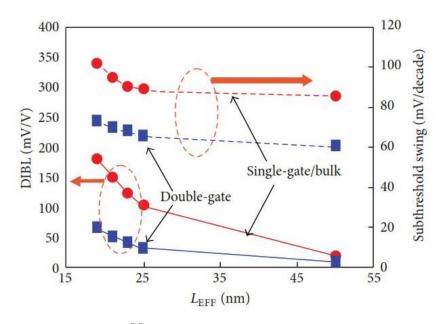

| Fig.2.2: Schematic of basic FinFET architecture (Bhattacharya & Jha, 2014)4         | 18 |

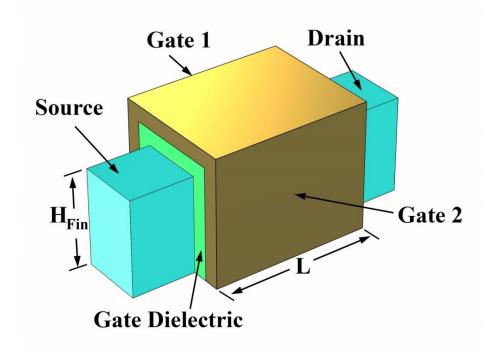

| Fig.2.3: Schematic of multi FinFET architecture (Ali Razavieh, Zeitzoff, & Nowak,   | ,  |

| 2019)                                                                               | 19 |

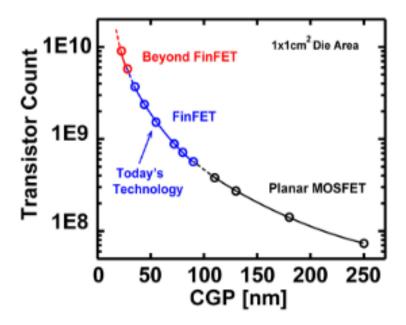

| Fig.2.4: Transformation of planar technology to FinFET technology CGP (Ali                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------|

| Razavieh et al., 2019)                                                                                                            |

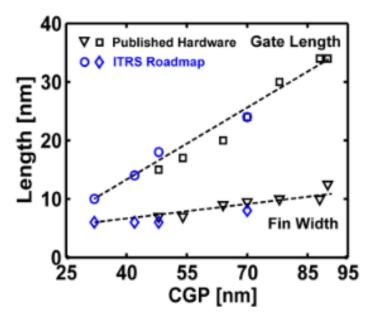

| Fig.2.5: Scaling pattern of gate-length and $W_{fin}$ Vs CGP for several FinFET                                                   |

| technologies (Ali Razavieh et al., 2019)51                                                                                        |

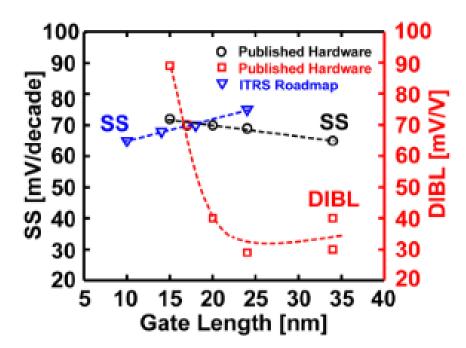

| Fig.2.6: Current trends of SS Vs CGP are likened to ITRS Roadmap specify                                                          |

| amplified SCEs in FinFETs. Experimental DIBL data likewise follows the trend                                                      |

| (A Razavieh, Zeitzoff, Brown, Karve, & Nowak, 2017)52                                                                             |

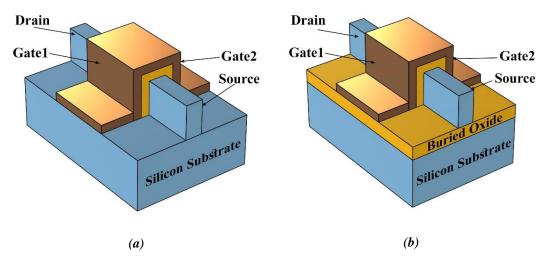

| Fig.2.7: Schematic diagram of (a) Bulk FinFET (b) SOI FinFET (Bhattacharya &                                                      |

| Jha, 2014)                                                                                                                        |

| Fig.2.8: Anatomy of (a) SG-FinFET (b) IG-FinFET (Bhattacharya & Jha, 2014) 57                                                     |

| Fig.2.9: Cross-sectional view of ADSE FinFET (Goel et al., 2010)                                                                  |

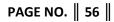

| Fig.2.10: Anatomy of DG-FinFET (Maurya & Bhowmick, 2021)                                                                          |

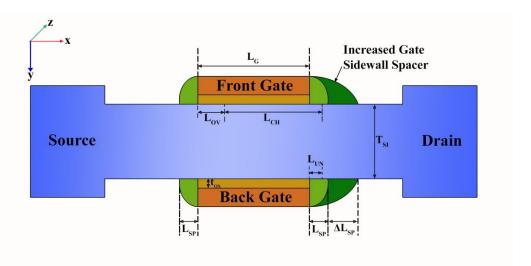

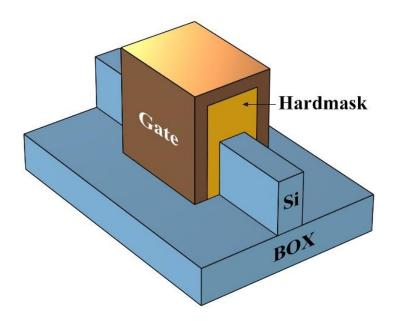

| Fig.2.11: Anatomy of TG-FinFET (Maurya & Bhowmick, 2021)                                                                          |

| Fig.2.12: Anatomy of SHS hybrid FinFET (Pradhan & Sahu, 2016)                                                                     |

| Fig.2.13: Anatomy of QFinFET (Maity, Maity, Maity, & Baishya, 2019)66                                                             |

| Fig.2.14: Anatomy of stacked-gate FinFET75                                                                                        |

| Fig.2.15: Anatomy of trench-Fe-FinFET                                                                                             |

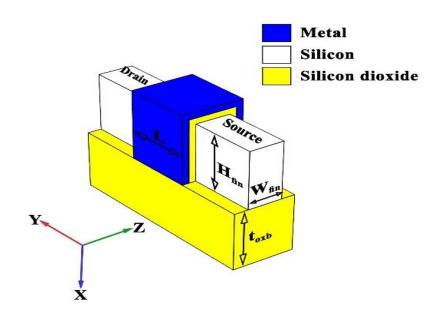

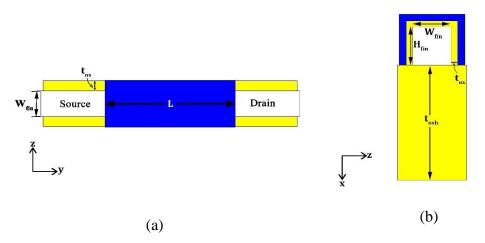

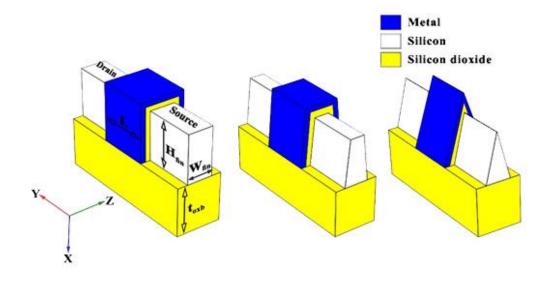

| Fig.3.1: Structure of TG-FinFET                                                                                                   |

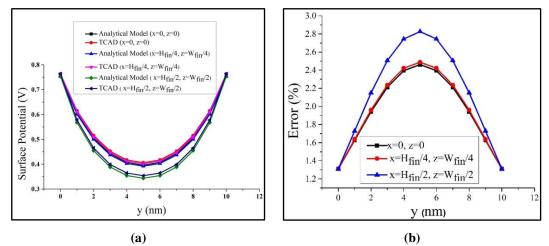

| Fig.3.2: Cross-sectional view of TG-FinFET along (a) y-z plane (b) x-z plane83                                                    |

|                                                                                                                                   |

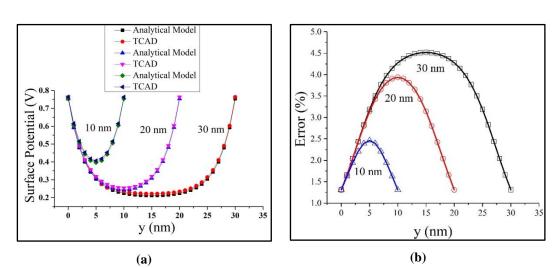

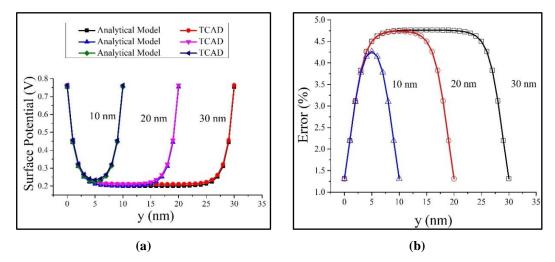

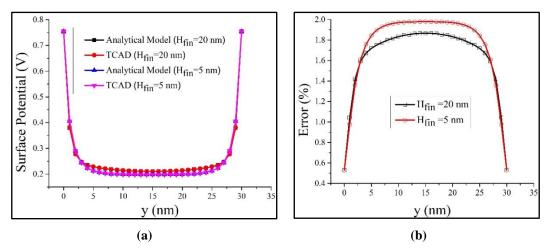

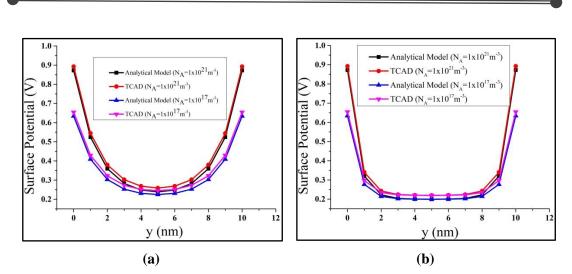

| Fig.3.3: At three different channel lengths for SiO <sub>2</sub> (a) Change of $\Phi$ along the                                   |

| Fig.3.3: At three different channel lengths for $SiO_2$ (a) Change of $\Phi$ along the channel (b) Percentage error along channel |

|                                                                                                                                   |

| channel (b) Percentage error along channel                                                                                        |

| channel (b) Percentage error along channel                                                                                        |

| <ul> <li>channel (b) Percentage error along channel</li></ul>                                                                     |

| <ul> <li>channel (b) Percentage error along channel</li></ul>                                                                     |

| <ul> <li>channel (b) Percentage error along channel</li></ul>                                                                     |

| <ul> <li>channel (b) Percentage error along channel</li></ul>                                                                     |

| <ul> <li>channel (b) Percentage error along channel</li></ul>                                                                     |

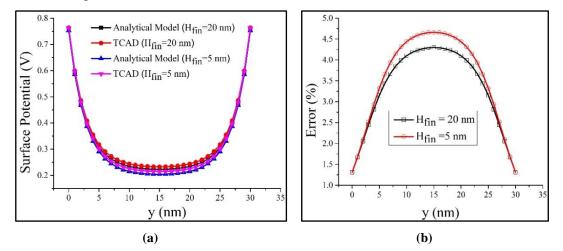

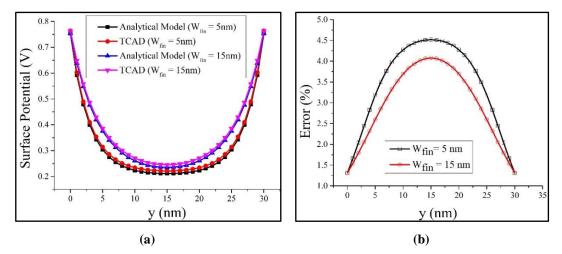

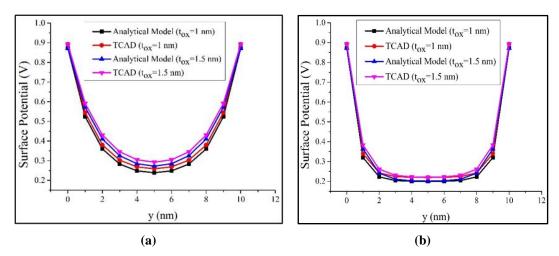

| Fig.3.9: For two fin widths for SiO <sub>2</sub> (a) Change of $\Phi$ along the channel (b)                                                                                                                                                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Percentage error of $\Phi$ along the channel                                                                                                                                                                                                                                                                                               |

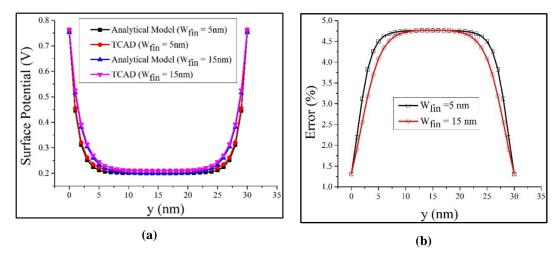

| Fig.3.10: For two fin widths for HfO <sub>2</sub> (a) Change of $\Phi$ along the channel (b)                                                                                                                                                                                                                                               |

| Percentage error of $\Phi$ along the channel                                                                                                                                                                                                                                                                                               |

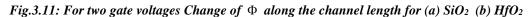

| Fig.3.11: For two gate voltages Change of $\Phi$ along the channel length for (a) SiO <sub>2</sub>                                                                                                                                                                                                                                         |

| (b) HfO <sub>2</sub>                                                                                                                                                                                                                                                                                                                       |

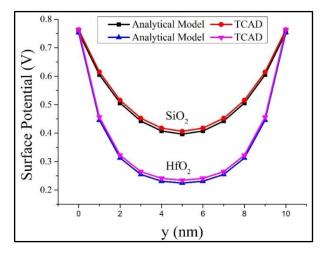

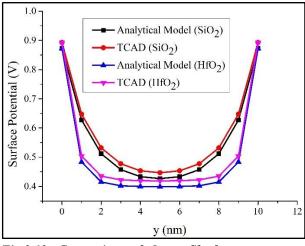

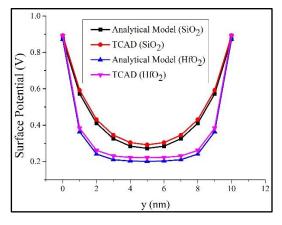

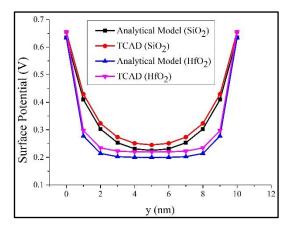

| Fig.3.12: Comparison of $\Phi$ profile for two separate dielectric materials 104                                                                                                                                                                                                                                                           |

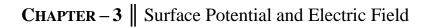

| Fig.3.13: For two drain voltages the change of $\Phi$ along the channel for (a) SiO <sub>2</sub> (b)                                                                                                                                                                                                                                       |

| HfO <sub>2</sub>                                                                                                                                                                                                                                                                                                                           |

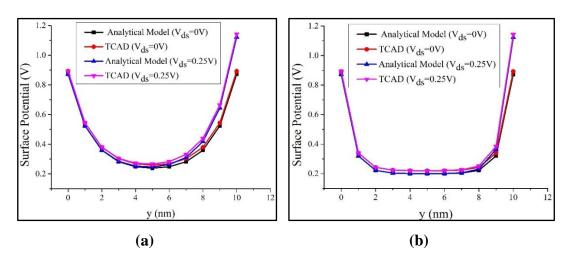

| Fig.3.14: Comparison of $\Phi$ along the channel for two dielectric materials 105                                                                                                                                                                                                                                                          |

| Fig.3.15: For two oxide thickness change of $\Phi$ down the channel length for (a) SiO <sub>2</sub>                                                                                                                                                                                                                                        |

| (b) HfO <sub>2</sub>                                                                                                                                                                                                                                                                                                                       |

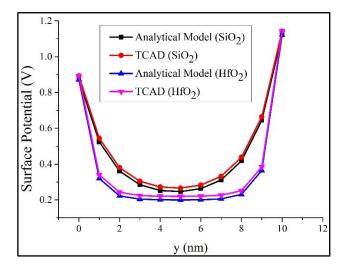

| Fig.3.16: Comparison of $\Phi$ profiles for different dielectric materials                                                                                                                                                                                                                                                                 |

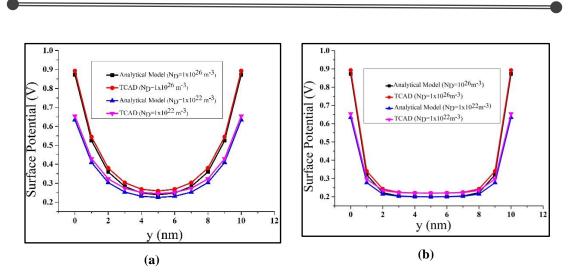

| Fig.3.17: At two source/drain doping concentrations change of $\Phi$ along the channel                                                                                                                                                                                                                                                     |

| for (a) SiO <sub>2</sub> (b) HfO <sub>2</sub>                                                                                                                                                                                                                                                                                              |

| Fig.3.18: Comparison of $\Phi$ profiles for different dielectric materials                                                                                                                                                                                                                                                                 |

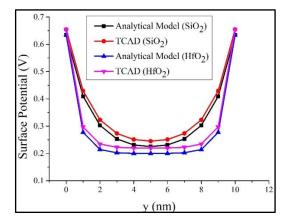

| Fig.3.19: At two substrate doping concentrations, change of $\Phi$ along the channel for                                                                                                                                                                                                                                                   |

| (a) SiO <sub>2</sub> (b) HfO <sub>2</sub>                                                                                                                                                                                                                                                                                                  |

| Fig.3.20: Comparative study of change of $\Phi$ down the channel length for SiO <sub>2</sub> and                                                                                                                                                                                                                                           |

| HfO <sub>2</sub>                                                                                                                                                                                                                                                                                                                           |

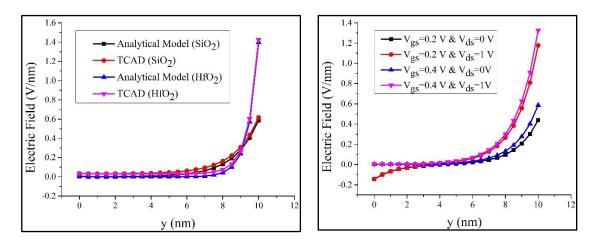

| Fig.3.21: Comparison of Electric Field for SiO <sub>2</sub> and HfO <sub>2</sub> 109                                                                                                                                                                                                                                                       |

| Eig 2 22: Electric field along the shannel for SiO at two gets voltages and two drain                                                                                                                                                                                                                                                      |

| Fig.3.22: Electric field along the channel for $SiO_2$ at two gate voltages and two drain                                                                                                                                                                                                                                                  |

| voltages                                                                                                                                                                                                                                                                                                                                   |

| voltages                                                                                                                                                                                                                                                                                                                                   |

| voltages                                                                                                                                                                                                                                                                                                                                   |

| voltages                                                                                                                                                                                                                                                                                                                                   |

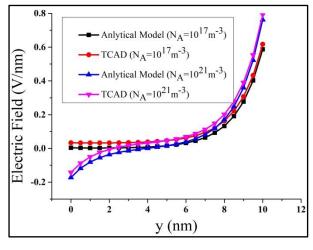

| voltages109Fig.3.23: The electric field along the channel lengths for SiO2 at two channel doping<br>concentration109Fig.4.1: Extraction of $V_T$ using constant current method113                                                                                                                                                          |

| voltages109Fig.3.23: The electric field along the channel lengths for SiO2 at two channel doping<br>concentration109Fig.4.1: Extraction of $V_T$ using constant current method113Fig.4.2: Extraction of $V_T$ using the linear extrapolation method114                                                                                     |

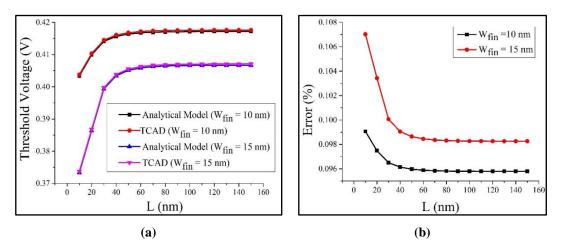

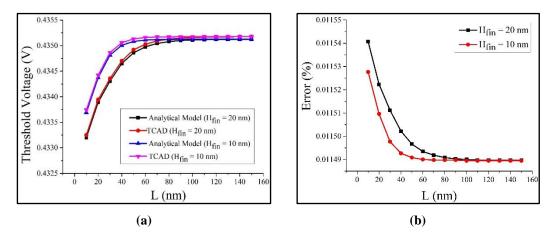

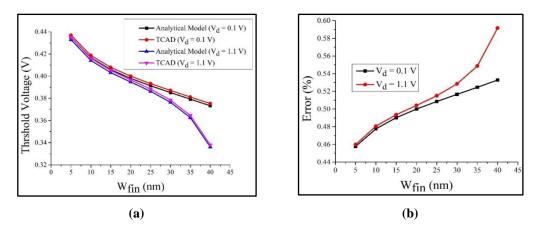

| voltages109Fig.3.23: The electric field along the channel lengths for SiO2 at two channel doping<br>concentration109Fig.4.1: Extraction of $V_T$ using constant current method113Fig.4.2: Extraction of $V_T$ using the linear extrapolation method114Fig.4.3: For SiO2 at different $W_{fin}$ (a) Change of $V_T$ with channel length (b) |

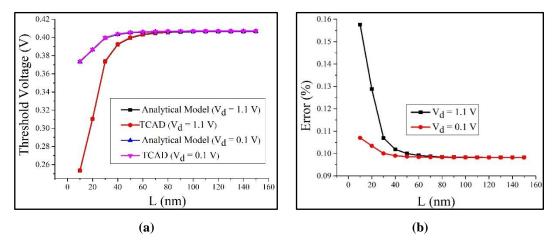

| Fig.4.5: For SiO <sub>2</sub> at different drain voltage (a) Change of $V_T$ with channel length (b)       |

|------------------------------------------------------------------------------------------------------------|

| Percentage error of $V_T$ with channel length                                                              |

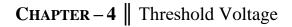

| Fig.4.6: $V_T$ with channel length (a) Comparison between SiO <sub>2</sub> and HfO <sub>2</sub> (b)        |

| Percentage error                                                                                           |

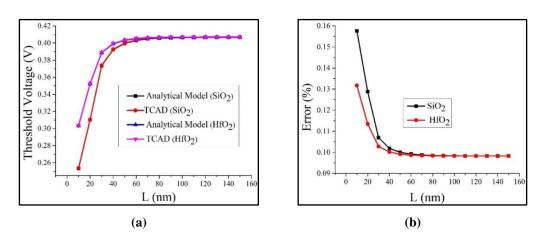

| Fig.4.7: For SiO <sub>2</sub> at different drain voltage (a) Change of $V_T$ with $W_{fin}$ (b)            |

| Percentage error of $V_T$ with $W_{fin}$                                                                   |

| Fig.4.8: For HfO <sub>2</sub> at different drain voltage (a) Change of $V_T$ with $W_{fin}$ (b)            |

| Percentage error of $V_T$ with $W_{fin}$                                                                   |

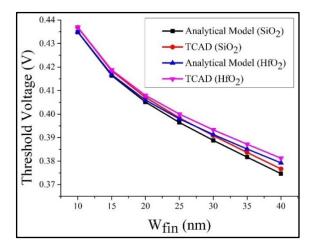

| Fig.4.9: Comparison of $V_T$ for SiO <sub>2</sub> and HfO <sub>2</sub> with device parameters $L = 40$ nm, |

| $H_{fin} = 20 \text{ nm and } v_d = 0.1 \text{ V}$                                                         |

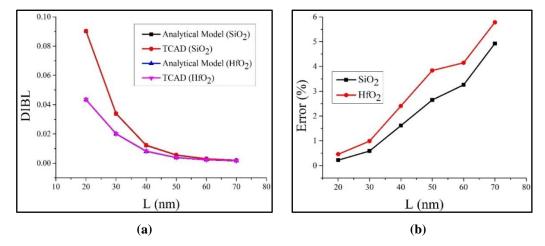

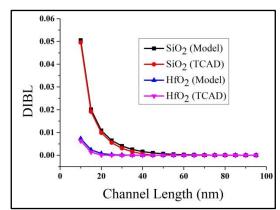

| Fig.4.10: DIBL with channel length (a) Comparison between $SiO_2$ and $HfO_2$ (b)                          |

| Percentage error                                                                                           |

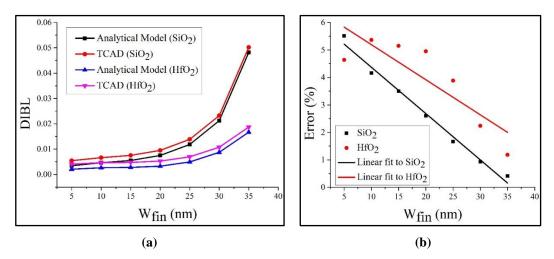

| Fig.4.11: DIBL with $W_{fin}$ (a) Comparison between SiO <sub>2</sub> and HfO <sub>2</sub> (b) Percentage  |

| error                                                                                                      |

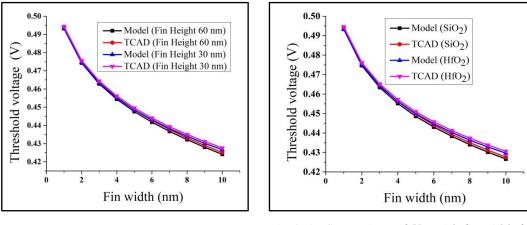

| Fig.4.12: The change of $V_T$ with $W_{fin}$ for different fin heights for SiO <sub>2</sub> 131            |

| Fig.4.13: Comparison of $V_T$ with fin width for two dielectric gate oxide                                 |

| Fig.4.14: The change of $V_T$ with fin width for different channel lengths for SiO <sub>2</sub> .131       |

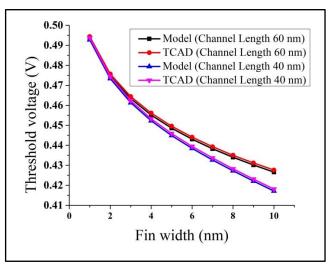

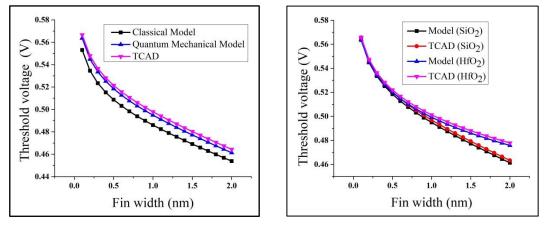

| Fig.4.15: Comparison of the classical and quantum mechanical model of threshold                            |

| voltage for SiO <sub>2</sub>                                                                               |

| Fig.4.16: Comparison of the quantum mechanical model of $V_T$ for two gate                                 |

| dielectric material                                                                                        |

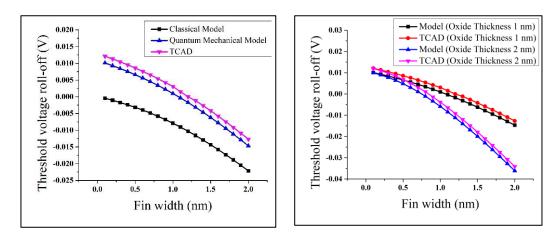

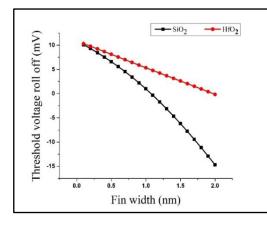

| Fig.4.17: Change of $\Delta V_T$ with fin width using the quantum mechanical model for                     |

| SiO <sub>2</sub> 133                                                                                       |

| Fig.4.18: Variation of $\Delta V_T$ with fin width using the quantum mechanical model for                  |

| SiO <sub>2</sub> 133                                                                                       |

| Fig.4.19: Comparison of $\Delta V_T$ with fin width using the quantum mechanical model                     |

| for both dielectric materials                                                                              |

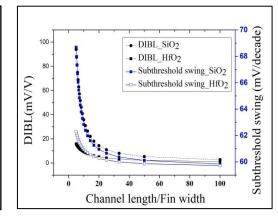

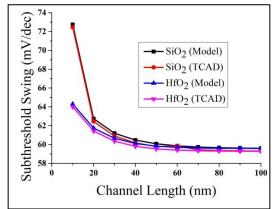

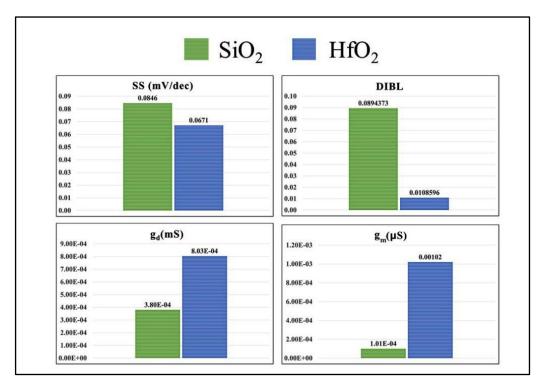

Fig.4.20: Effect of  $(L/W_{fin})$  ratio on DIBL and SS for both gate dielectric materials

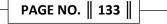

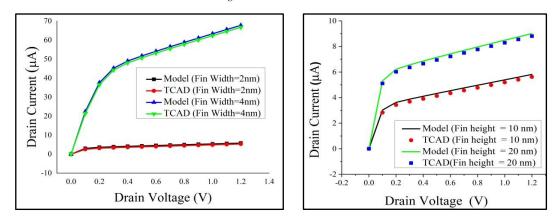

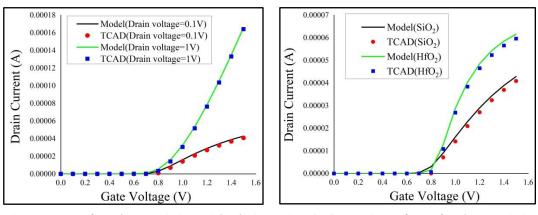

| Fig.5.1: Drain characteristics at different gate voltage for SiO <sub>2</sub> 147                         |

|-----------------------------------------------------------------------------------------------------------|

| Fig.5.2: Comparison of drain current for two gate oxides                                                  |

| Fig.5.3: Drain characteristics at two different fin widths at for $SiO_2$                                 |

| Fig.5.4: Drain characteristics at two different fin heights for $SiO_2$ 148                               |

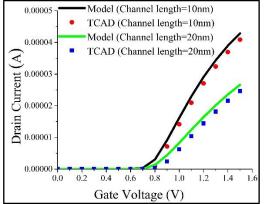

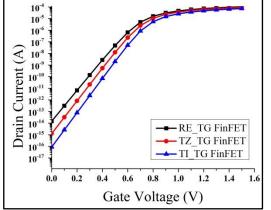

| Fig.5.5: Transfer characteristics at two distinct channel lengths, for $SiO_2$ 149                        |

| Fig.5.6: Transfer characteristics for various fin widths for SiO <sub>2</sub> 149                         |

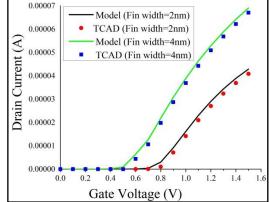

| Fig.5.7: Transfer characteristics with drain voltages as parameter for SiO <sub>2</sub> 149               |

| Fig.5.8: Comparison of transfer characteristics for two gate dielectrics149                               |

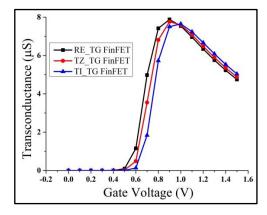

| Fig.5.9: Ttransconductance with $v_d$ for SiO <sub>2</sub>                                                |

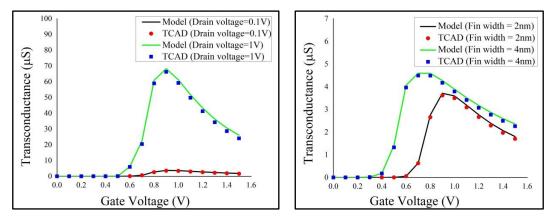

| Fig.5.10: Ttransconductance with two fin widths for SiO <sub>2</sub> 150                                  |

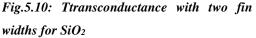

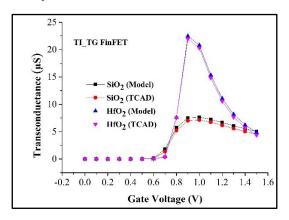

| Fig.5.11: Comparison of transconductance for two gate oxide materials                                     |

| Fig.5.12: Transconductance/ Drain current with gate voltage for SiO <sub>2</sub> 151                      |

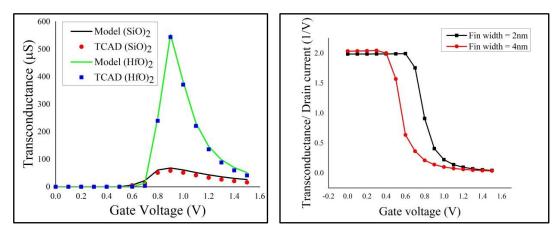

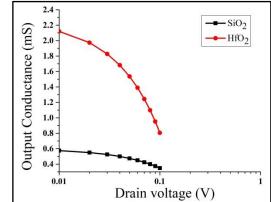

| Fig.5.13: Output conductance with channel length for $SiO_2$                                              |

| Fig.5.14: Output conductance with fin width for $SiO_2$                                                   |

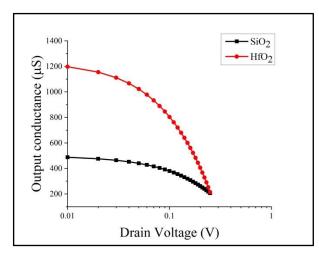

| Fig.5.15: The comparison of output conductance for two dielectric materials 153                           |

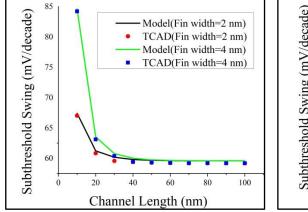

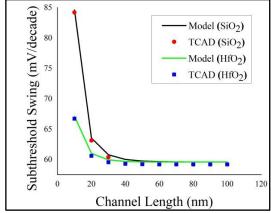

| Fig.5.16: Subthreshold swing with channel length at different fin widths153                               |

| Fig.5.17: Comparison of subthreshold swing for two dielectric materials153                                |

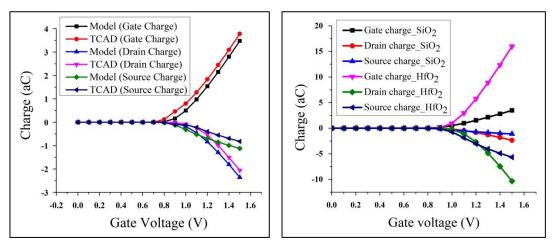

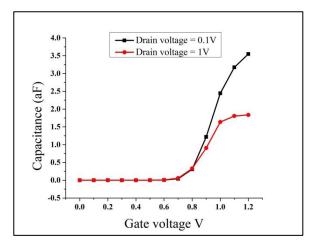

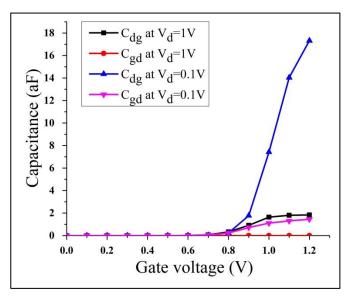

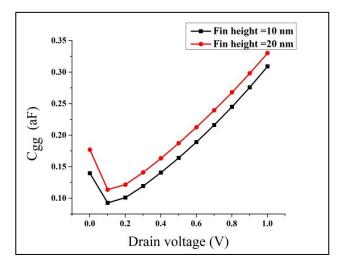

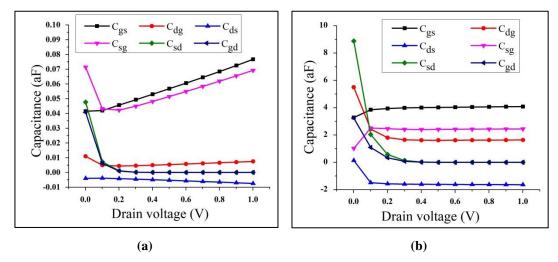

| Fig.6.1: The gate, drain and source terminal charge with gate voltage for $SiO_2 \dots 171$               |

| Fig.6.2: Comparison of the charges for SiO <sub>2</sub> and HfO <sub>2</sub> 171                          |

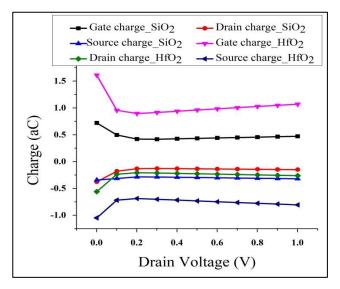

| Fig.6.3: Variation of charges with $v_d$ for both dielectrics                                             |

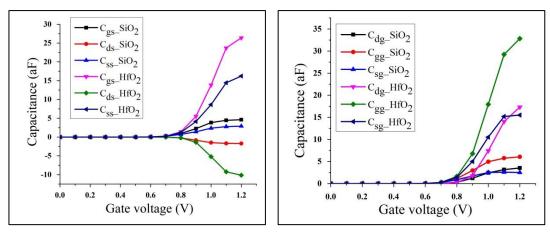

| Fig.6.4: Source related trans-capacitance at for $SiO_2$ and $HfO_2$ 172                                  |

| Fig.6.5: Gate related trans-capacitance at for $SiO_2$ and $HfO_2$                                        |

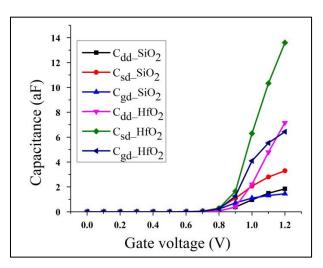

| Fig.6.6: Drain related trans-capacitance with gate voltage for $SiO_2$ and $HfO_2$ 172                    |

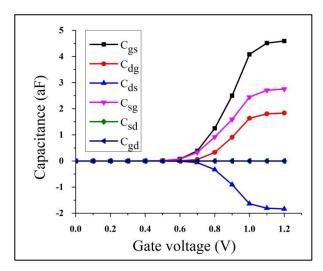

| Fig.6.7: Trans-capacitance with gate voltage for $SiO_2$                                                  |

| Fig.6.8: $C_{dg}$ variation with gate voltage with $v_d$ as a parameter for SiO <sub>2</sub> 173          |

| Fig.6.9: Change of $C_{gd}$ & $C_{dg}$ with gate voltage at different drain voltages for SiO <sub>2</sub> |

|                                                                                                           |

| Fig.6.10: Trans-capacitance variation with $v_d$ for SiO <sub>2</sub>                                     |

| Fig.0.11: Trans-capacitance variation with $v_d$ for SiO <sub>2</sub> when (a) $v_g = 0.6v$ (b) |

|-------------------------------------------------------------------------------------------------|

| $v_g = 1.0V$                                                                                    |

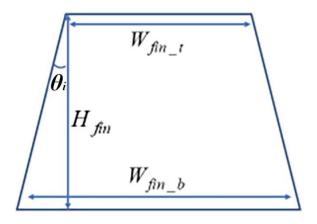

| Fig.7.1: Anatomy of three TG-FinFET 180                                                         |

| Fig.7.2: Cross-sectional view of trapezoidal FinFET                                             |

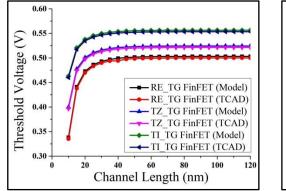

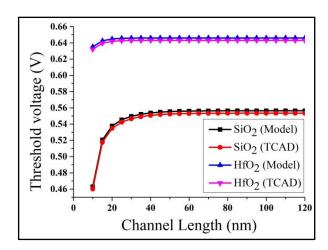

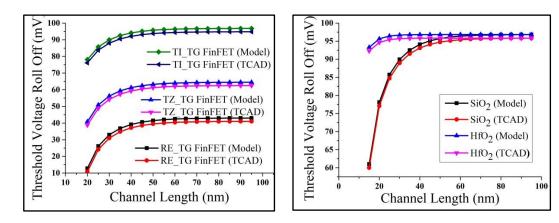

| Fig.7.3: Change of threshold voltage with channel length for SiO <sub>2</sub>                   |

| Fig.7.4: Change of threshold voltage with channel length for HfO <sub>2</sub>                   |

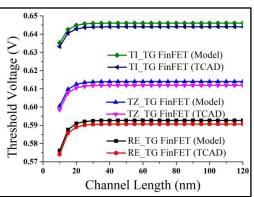

| Fig.7.5: Comparison of threshold voltage of two dielectric materials for TI-TG                  |

| FinFET                                                                                          |

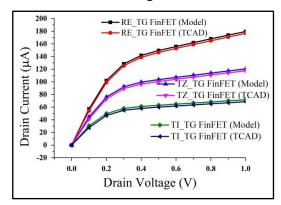

| Fig.7.6: Drain characteristics for SiO <sub>2</sub>                                             |

| Fig.7.7: Comparison of drain characteristics of two dielectric materials for TI-TG              |

| FinFET                                                                                          |

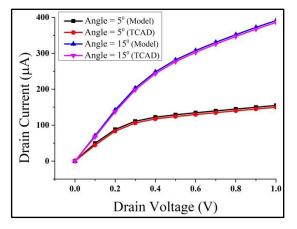

| Fig.7.8: Drain current for SiO <sub>2</sub> as a function of inclination angle for TZ-TG FinFET |

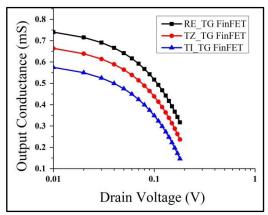

|                                                                                                 |

| Fig.7.9: Change of output conductance with drain voltage for SiO <sub>2</sub>                   |

| Fig.7.10: Comparison of output conductance of two dielectric materials for TI-TG                |

| FinFET                                                                                          |

| Fig.7.11: Transfer characteristics for SiO <sub>2</sub>                                         |

| Fig.7.12: Comparison of transfer characteristics of two dielectric materials for TI-TG          |

| FinFET                                                                                          |

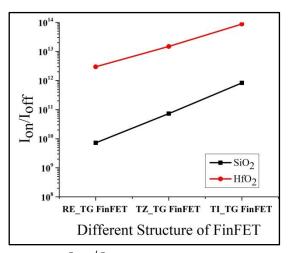

| Fig.7.13: $I_{ON}/I_{OFF}$ ratio for three fin shape structures                                 |

| Fig.7.14: Change of transconductance with gate voltage for SiO <sub>2</sub>                     |

| Fig.7.15: Comparison of transconductance of two dielectric materials for TI-TG                  |

| FinFET                                                                                          |

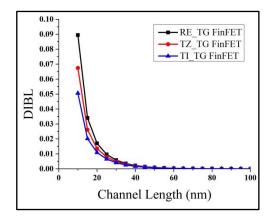

| Fig.7.16: Change of DIBL with channel length for SiO <sub>2</sub> 188                           |

| Fig.7.17: Comparison of DIBL of two dielectric materials for TI-TG FinFET 188                   |

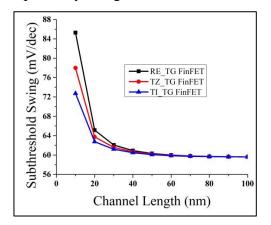

| Fig.7.18: Change of subthreshold swing with channel length for SiO <sub>2</sub> 188             |

| Fig.7.19: Comparison of sub threshold swing of two dielectric materials for TI-TG               |

| FinFET                                                                                          |

| Fig.7.20: Change of $\Delta V_T$ with channel length for SiO <sub>2</sub>                       |

| Fig.7.21: Comparison $\Delta V_T$ of two dielectric materials for TI-TG FinFET                  |

Fig.6.11: Trans-capacitance variation with  $v_d$  for SiO<sub>2</sub> when (a)  $v_g = 0.6V$  (b)

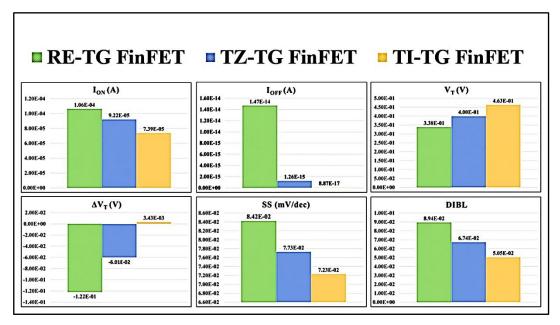

| Fig.8.1: A comparative study of different parameters for RI | E-TG FinFET, TZ-TG       |

|-------------------------------------------------------------|--------------------------|

| FinFET & TI-TG FinFET                                       |                          |

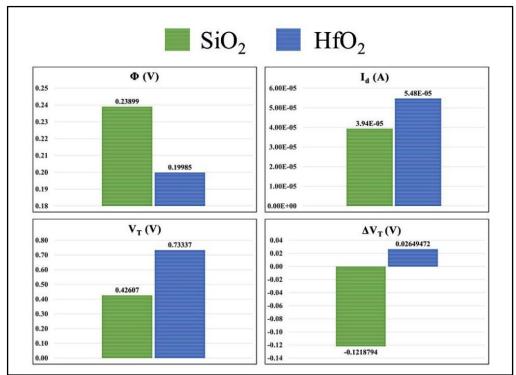

| Fig.8.2: Comparison of different parameters of RE-TG Finl   | FET for both dielectric  |

| materials                                                   |                          |

| Fig.8.3: Comparison of rest of the parameters of RE-TG Fig. | nFET for both dielectric |

| materials                                                   |                          |

| <br>PAGE NO.    12 |  |

|--------------------|--|

|                    |  |

## **List of Tables**

#### Page No.

| Table 1.1: Scaling Rules (Dennard et al., 1974)                                | 22   |

|--------------------------------------------------------------------------------|------|

| Table 1.2: Parameters of few high-k materials with respect to Si (Robertson, 2 | 000; |

| HS. P. Wong, 2005)                                                             | 40   |

| Table 3.1: Design Parameter Values for Surface Potential                       | 99   |

| Table 4.1: Design Parameter Values for Threshold Voltage                       | 125  |

| Table 5.1: Design Parameter Values for Drain Current                           | 146  |

| Table 6.1: Design Parameter Values for Trans-Capacitance                       | 170  |

| Table 7.1: Design Parameters Values for Fin Shaped Based Study                 | 182  |

| Table 7.2: $\lambda_{eff}$ for Three Different Shaped FinFET                   | 190  |

| PAGE NO. | 13 |  |

|----------|----|--|

|----------|----|--|

## Abbreviation

| #      |                                         |

|--------|-----------------------------------------|

| 2-D    | Two Dimensional                         |

| 3-D    | Three Dimensional                       |

| Α      |                                         |

| ADSE   | Asymmetric drain-spacer-extended        |

| ASG    | Asymmetric gate-work function           |

| B      |                                         |

| BSIM   | Berkeley Short-Channel IGFET Model      |

| BJT    | Bipolar junction transistor             |

| BOX    | Buried oxide                            |

| BTI    | Bias temperature instability            |

| С      |                                         |

| CAD    | Computer-aided design                   |

| CD     | Critical dimension                      |

| CGP    | Contacted gate pitch                    |

| CLM    | Channel length modulation               |

| CMC    | Compact Model Council                   |

| CMG    | Common multi-gate                       |

| CMOS   | Complementary metal-oxide-semiconductor |

| CPU    | Central processing unit                 |

| Cy-GAA | Cylindrical Gate-All-Around             |

| D      |                                         |

| DELTA  | Depleted lean-channel transistor        |

| DG     | Double-gate                             |

| DIBL   | Drain induced barrier lowering          |

| DT     | Direct tunnelling                       |

| DTCO   | Design technology co-optimization       |

| F      |                                         |

## E

| EGA | Extended gate area         |

|-----|----------------------------|

| EOT | Equivalent oxide thickness |

## F

| FD         | Fully depleted                    |

|------------|-----------------------------------|

| Fe-FinFETs | Ferroelectric FinFET              |

| FET        | Field-effect transistor           |

| FIBL       | Fringing induced barrier lowering |

| FOM        | Figures Of Merit                  |

## G

| GAA  | Gate-all-around            |

|------|----------------------------|

| GIDL | Gate induced drain leakage |

| GS   | Gate-stacked               |

## Η

| Hot carrier injection     |

|---------------------------|

| High-k/metal-gate         |

| High performance          |

| High-volume manufacturing |

|                           |

## I

| IC     | Integrated circuit                                  |

|--------|-----------------------------------------------------|

| IFT    | International Focus Team                            |

| IG     | Independent-Gate                                    |

| IGFET. | Insulated Gate Field Effect Transistors             |

| IL     | Interfacial-layer                                   |

| IMG    | Independent-multigate                               |

| IRDS   | International Roadmap for Devices and Systems       |

| ITRS   | International Technology Roadmap for Semiconductors |

|        |                                                     |

## L

| LDD  | Lightly Doped Drain     |

|------|-------------------------|

| LER  | Line-edge roughness     |

| LOP  | Low operating power     |

| LSI  | Large scale integration |

| LSTP | Low standby power       |

## M

| MAC      | Multiply-accumulate              |

|----------|----------------------------------|

| M-FinFET | Multiple fins constructed FinFET |

| MG     | Multi-gate                                        |

|--------|---------------------------------------------------|

| MIGFET | Multiple Independent Gate FET                     |

| MOSFET | Metal oxide semiconductor Field-Effect Transistor |

## Ν

| NBTI      | Negative bias temperature instability |

|-----------|---------------------------------------|

| NC-FinFET | Negative capacitance FinFET           |

| NMOS      | n-channel metal-oxide semiconductor   |

## P

| PBTI | Positive bias temperature instability |

|------|---------------------------------------|

| PD   | Partially depleted                    |

| PMOS | P-channel metal-oxide semiconductor   |

| PPAC | Power, performance, area, and cost    |

## Q

| QFinFET | Quantum FinFET            |

|---------|---------------------------|

| QG      | Quadruple-gate            |

| QM      | Quantum mechanical        |

| QME     | Quantum mechanical effect |

## R

| RCS              | Remote coulomb scattering                |

|------------------|------------------------------------------|

| RDF              | Resist-defined fin                       |

| <b>RE-FinFET</b> | Rectangular FinFET                       |

| RE-GAA           | Rectangular Gate-All-Around              |

| RFID             | Radio-frequency identification           |

| RGG              | Ratio of average grain size to gate area |

| RPS              | Remote phonon scattering                 |

| RTA              | Rapid thermal annealing                  |

| S                |                                          |

| SCE              | Short channel effect                     |

| SDF              | Spacer-defined fin                       |

| SG               | Shorted-Gate                             |

| SHS              | Symmetric high-k spacer                  |

| SOI              | Silicon On Insulator                     |

| SR               | Surrounding gate                         |

| SRAM             | Static random access memory              |

Т

| TCAD             | Technology computer-aided design            |

|------------------|---------------------------------------------|

| TDDB             | Time-dependent dielectric breakdown         |

| TG               | Triple-gate                                 |

| TGF              | Transconductance generation factor          |

| <b>TI-FinFET</b> | Triangular FinFET                           |

| TMD ML           | Transitional metal dichalcogenide monolayer |

| TZ-FinFET        | Trapezoidal FinFET                          |

## U

| ULSI | Ultra-scale integration |

|------|-------------------------|

| UTB  | Ultra-thin body         |

| UTBB | Ultra-thin body and box |

| VLSI Very-large-scale integration |  |

|-----------------------------------|--|

|-----------------------------------|--|

# V VLS W

| WFV | Work function | variation |

|-----|---------------|-----------|

|     |               |           |

| <br>PAGE NO.    17 | ] |

|--------------------|---|

|                    |   |

## Symbols

| Symbol                  | Parameter Name                             |

|-------------------------|--------------------------------------------|

| V <sub>sub</sub>        | Back gate potential                        |

| $N_A$                   | Body doping concentration of acceptor atom |

| K                       | Boltzmann constant                         |

| $v_{bi}$                | Build-in potential                         |

| L                       | Channel length                             |

| k                       | Dielectric constant                        |

| $Q_d$                   | Drain charge                               |

| $I_d$                   | Drain current                              |

| <i>v<sub>dsat</sub></i> | Drain saturation voltage                   |

| $v_d$                   | Drain voltage                              |

| $L_{e\!f\!f}$           | Effective channel length                   |

| $V_{def}$               | Effective drain voltage                    |

| $W_{e\!f\!f}$           | Effective fin width                        |

| $\mu_{\it eff}$         | Effective mobility                         |

| $\lambda_{e\!f\!f}$     | Effective natural length                   |

| ε <sub>0</sub>          | Electric permittivity of free space        |

| $v_q$                   | Electron quasi-fermi potential             |

| q                       | Electronic charge                          |

| ${H}_{fin}$             | Fin height                                 |

| $W_{fin}$               | Fin width                                  |

| v <sub>fb</sub>         | Flat band voltage                          |

| Symbol                 | Parameter Name                                   |

|------------------------|--------------------------------------------------|

| $m_0$                  | Free electron mass                               |

| $\mathcal{Q}_{g}$      | Gate charge                                      |

| $t_{ox}$               | Gate oxide thickness                             |

| $\mathcal{V}_{gs}$     | Gate to source voltage                           |

| $v_g$                  | Gate voltage                                     |

| n <sub>i</sub>         | Intrinsic carrier concentration                  |

| $Q_{inv}$              | Inversion sheet charge density                   |

| $m^{*}$                | Isotropic effective mass of the electron         |

| μ                      | Mobility of charge                               |

| λ                      | Natural length                                   |

| $\lambda_{asym}$       | Natural length of asymmetric DG-FinFET           |

| $\lambda_{sym}$        | Natural length of symmetric DG-FinFET            |

| $q_{ip}$               | Normalised sheet charge density                  |

| $g_d$                  | Output/drain conductance                         |

| $C_{ox}$               | Oxide capacitance per unit area                  |

| ε <sub>ox</sub>        | Permittivity of dielectric medium / insulator    |

| ε <sub>si</sub>        | Permittivity of silicon                          |

| $v_{sat}$              | Saturation velocity                              |

| $Q_{ip}$               | Sheet charge density                             |

| t <sub>oxb</sub>       | Silicon dioxide thickness                        |

| $Q_s$                  | Source charge                                    |

| v <sub>s</sub>         | Source voltage                                   |

| $N_D$                  | Source/ Drain doping concentration of donor atom |

| η                      | Subthreshold swing coefficient                   |

| Φ                      | Surface potential                                |

| <i>v</i> <sub>th</sub> | Thermal voltage                                  |

| $Q_{th}$               | Threshold charge density                         |

| Symbol       | Parameter Name                                  |

|--------------|-------------------------------------------------|

| $V_T$        | Threshold voltage                               |

| $\Delta V_T$ | Threshold voltage roll-off                      |

| $g_m$        | Transconductance                                |

| $\phi_{ms}$  | Work function difference of metal-semiconductor |

| SS           | Subthreshold swing                              |

| <br>PAGE NO.    20 |  |

|--------------------|--|

|                    |  |

## CHAPTER - 1

### Introduction

#### **1.1. Background**

The electronic era of semiconductors was steered by the discovery of the bipolar junction transistor (BJT) in 1948 by Bardeen, Brattain, and Shockley at the Bell Telephone Laboratories (Ross, 1998). It was accelerated by creating an integrated circuit (IC) in 1958 by Jack Kilby in Texas Instruments (Ross, 1998). Being lightweight and small, ICs are widely used in different electronic components, viz., microprocessors, memory devices, radar etc., so that the dimension of the electronic system is reduced to a few square centimetres. The development of IC technology matures large-scale integration (LSI), very-large-scale integration (VLSI), and ultrascale integration (ULSI). With this advancement of IC technology, semiconductor devices are now an integral part of our day-to-day lives.

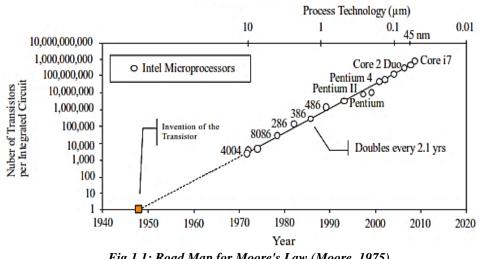

Initially, the number of transistors increases exponentially with time. In 1965, Gordon Moore first noticed and forecasted that the amount of transistors fabricated within an IC increases twice every two consecutive years (Moore, 1975). The aforesaid emerging movement acknowledged as Moore's law became a golden rule of the semiconductor industry. The law is demonstrated in Fig.1.1 with the help of the Intel chronological processors. Here, the number of transistors in the successive processors is plotted against time (Dubash, 2005; Markoff, 2005).

Fig.1.1: Road Map for Moore's Law (Moore, 1975)

The notion of scaling is to scale up the doping concentration and scale down device voltages and sizes using the same factor. Table 1.1 shows the scaling guidelines in tabular format.

| Physical Parameters                 | Consistent<br>electric Field<br>scaling factor | General<br>scaling<br>factors | General<br>selective<br>scaling factors                             |

|-------------------------------------|------------------------------------------------|-------------------------------|---------------------------------------------------------------------|

| Insulator thickness, Channel length | $1/\alpha_0$                                   | $1/\alpha_o$                  | $1/\alpha_o$                                                        |

| Wiring width, channel width         | $1/\alpha_0$                                   | $1/\alpha_o$                  | $1/\alpha_{O_w}$                                                    |

| Electric Field in device            | 1                                              | Е                             | E                                                                   |

| Voltage                             | $1/\alpha_0$                                   | $\varepsilon/lpha_{O}$        | $\varepsilon/lpha_{O_{-d}}$                                         |

| On-current per device               | $1/\alpha_o$                                   | $\varepsilon/lpha_{O}$        | $\varepsilon/lpha_{O_w}$                                            |

| Doping                              | Α                                              | εα <sub>0</sub>               | $\mathcal{E}\alpha_{\mathrm{O}_{d}}$                                |

| Area                                | $1/\alpha_o^2$                                 | $1/\alpha_o^2$                | $1/\alpha_{O_w}^2$                                                  |

| Capacitance                         | $1/\alpha_{O}$                                 | $1/\alpha_o$                  | $1/\alpha_{O_w}$                                                    |

| Gate delay                          | $1/\alpha_o$                                   | $1/\alpha_o$                  | $1/\alpha_{O_d}$                                                    |

| Power dissipation                   | $1/\alpha_o^2$                                 | $\varepsilon^2/\alpha_o^2$    | $\varepsilon^2/\alpha_{O_w}\alpha_{O_d}$                            |

| Power density                       | 1                                              | $\varepsilon^2$               | $\varepsilon^2 \cdot \alpha_{\mathrm{O}_w} / \alpha_{\mathrm{O}_d}$ |

Table 1.1: Scaling Rules (Dennard et al., 1974)

These principles merely give us instructions to compress a device (Dennard et al., 1974). However, they do not say how small the gadgets can be produced. According to (Dennard et al., 1974),  $\alpha_0$  is the scaling parameter of dimension,  $\varepsilon$  is the electric field scaling parameter,  $\alpha_d$  indicates the gate length of the device and vertical dimension. Here,  $\alpha_0_w$  relates to the width and wiring of the device.

To maintain power, performance, area, and cost (PPAC) scaling for mobility  $(\mu)$ , big data, and cloud (e.g., IOT and server) implementation, the More Moore International Focus Team (IFT) of the International Roadmap for Devices and Systems (IRDS) specifies the electrical, physical, and reliability requirements for logic and memory technologies. This has been done for mainstream/high-volume manufacturing (HVM) over 15 years.

Semiconductor device manufacturing is dedicated mainly to digital logic, which must offer two types of devices: 1) high-performance logic and 2) densely packed low-power logic; speed, power, density, and affordability are all important considerations for this technology platform. The More Moore idea lays out a strategy for metal oxide semiconductor field-effect transistor (MOSFET) miniaturisation to sustain historical patterns of improving device performance at lower power and cost.

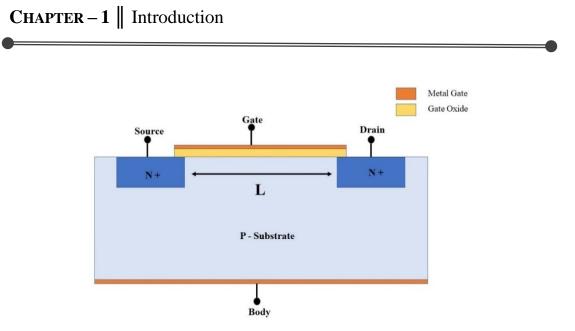

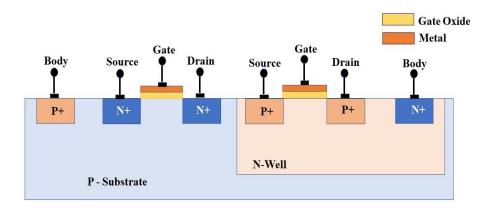

Initially, the BJT fabrication was hindered due to uneven surface passivation of the semiconductor. To solve this problem, Kahng, D and his team found a new device, field-effect transistor (FET) (Kahng, 1960). A few years later, in 1963, the idea of MOSFET was developed by Hofstein, S. R., & Heiman, F. P. (Hofstein & Heiman, 1963). Wanlass, F. M., & Sah, C. T. proposed a complementary metal-oxidesemiconductor (CMOS) circuit in the same year (Wanlass & Sah, 1991). Since that time, CMOS has seized control of the semiconductor market. The cross-sectional structure of MOSFET and CMOS is given in Fig.1.2 and Fig.1.3, respectively.

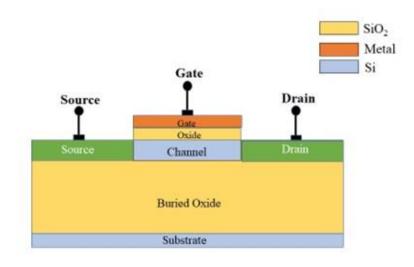

In 1980, the sub-micron dimension boundary was overcome. At the end of the '90s, an excellent improvement in device performance was achieved by using a new substrate, silicon on insulator (SOI). The SOI MOS construction is given in Fig.1.4.

Fig.1.2: Cross-sectional structure of MOSFET (D. Das, 2015)

Fig.1.3: Cross-sectional structure of CMOS (Chattopadhyay, 2006)

The top silicon film is a high-quality single-crystal appropriate for a high packing density, high-performance circuit. The buried oxide (BOX) beneath the single-crystal reduces capacitance to the Si layer, i.e., base wafer or supporting substrate. The BOX layer also provides better isolation, low leakage current and most importantly reduces the short channel effects (SCEs). SOI MOSFET operates in either partially depleted (PD) or fully depleted (FD) modes. In FD-SOI mode, the thin silicon layer acting as a channel which is depleted of the majority carriers. On the other hand, PD-SOI transistors are fabricated on reasonably thick silicon layers, higher than the depletion width. The PD-SOI MOSFET's kink effect or floating body effect causes

higher current consumption. The small subthreshold swing (SS) (Berger et al., 1999), high speed and reduced power consumption make the FD device more popular than the PD device. It is also free from the kink effect (Cristoloveanu & Li, 1995). Different dielectric materials and base wafers are also reported to produce other varieties of SOI structures.

Fig.1.4: Cross-sectional view of SOI MOSFET structure (D. Das, 2015)

#### **1.2. Short Channel Effects**

SCEs are the sequence of events associated with the miniaturisation of the device dimension. It includes velocity saturation  $(v_{sat})$ , drain induced barrier lowering (DIBL), threshold voltage roll-off  $(\Delta V_T)$ , mobility degradation, hot carrier effect and most importantly, high leakage current.

#### 1.2.1 Velocity saturation and Mobility degradation

The longitudinal electric field is assumed to be significantly small in the long channel device. So, the carrier velocity is proportional to the field. But this assumption is not effective in short channel devices and the velocity saturates with the electric field, which is illustrated in Fig.1.5.

The effect on device characteristics due to the lack of proportionality between these two parameters is known as the velocity saturation effect. The short channel device's drain current  $(I_d)$  depends on gate length rather than the gate voltage  $(v_g)$ , it may saturate at lower voltage (J.-W. Han, C.-H. Lee, D. Park, & Y.-K. Choi, 2007; Hwang et al., 2009; H. Wong & Poon, 1997).

Fig.1.5: Representing velocity saturation  $(v_{sat})$  (D. Das, 2015)

The carrier movement in a particular direction is taking place in the semiconductors due to the presence of external bias. The velocity of the carriers is linearly proportionate to the applied electric field, commonly identified as  $\mu$ . But this relation is ineffective at a high electric field and carriers' velocity gets saturated, as depicted in Fig.1.5. The collision of the charge carriers with the interface degrades the carriers'  $\mu$  at the electric field in the range of 10<sup>5</sup> to 10<sup>7</sup> V/cm. The gradual channel approximation is invalid in the short channel device and increased vertical field results in carrier scattering adjacent to the surface. Therefore,  $\mu$  degradation is a noticeable effect in a short channel device.

#### 1.2.2 Drain induced barrier lowering

The field lines begin at the source and the drain ends at the channel if the width of space charge region of the drain and source is comparable to the length of the channel. Hence, with the increment of drain voltage  $(v_d)$ , drain field penetrates

through the channel to the source, reducing the barrier drastically; consequently,  $v_d$  regulates the threshold voltage  $(V_T)$ . This event is known as DIBL. The DIBL is shown in Fig.1.6. E<sub>c</sub>(y) indicates the conduction band energy and the channel is along the y-direction.

Fig.1.6: Bending of conduction due to DIBL (Yannis Tsividis, 1987)

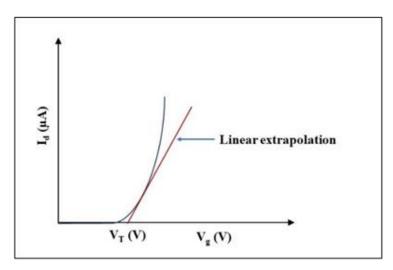

#### 1.2.3 Threshold voltage roll-off

Traditionally,  $V_T$  reduction with the diminution of the gate length is a renowned SCE called  $\Delta V_T$ , which arises as a consequence of the restriction of gate control over the channel. Hence,  $I_d$  increases with the decrement of  $V_T$ . At  $v_g = 0$  V i.e., in cut-off region, the  $(v_{gs} - V_T)$  produces a small negative voltage, which produces a large leakage current and leakage power. Here,  $v_{gs}$  is the gate to source voltage. This effect will be further enhanced with an increment of  $v_d$ .  $\Delta V_T$  is shown in Fig.1.7.

#### 1.2.4 Channel length modulation

Instead of a parallel curve in the saturation zone, the short channel device generates drain characteristics curves with a positive slope. Hence, this is the indication of SCE and it is to be calculated and addressed as channel length modulation (CLM). As the device enters into the saturation, the inversion charge density reduces and the velocity of the charge carriers increases to support the current. At a certain  $v_d$

, the carriers near the drain region attain a saturation velocity and carrier density reaches its minimum value. With the increment of  $v_d$ , the region mentioned above extends into the channel and is filled with acceptor atom concentration  $(N_A)$ . Hence, the actual channel length (L) decreases with the increment of  $v_d$ . Hence, CLM is the term used to describe this type of channel modification with  $v_d$ . Fig.1.8 depicts the CLM.

L (nm)

Fig.1.7: Representing  $\Delta V_T$  (Sze, Li, & Ng, 2021)

Fig.1.8: Block diagram representing channel length modulation

| <br>PAGE NO.    28 |  |

|--------------------|--|

|                    |  |

#### 1.2.5 Punch through

The extreme case of CLM is punch through. In this condition, the space charge regions around the source and drain fuse all together and form a single depletion region. It causes rapid growth of  $I_d$  with the small increment of drain to source voltage. This event is visualised in Fig.1.9. It will increase the output/drain conductance  $(g_d)$  and limit the maximum operating voltage (Y Taur & Ning, 1998).

Fig.1.9: Schematic diagram of punch through (Yannis Tsividis, 1987)

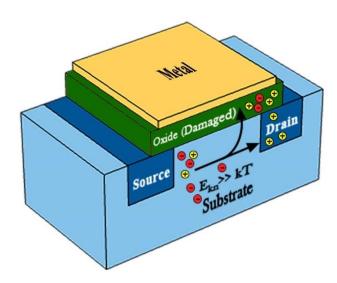

#### 1.2.6 Hot carrier effect

At reverse bias, the energetic electrons in the channel can tunnel the barrier and be trapped in the oxide layer. These trapped charges will modify the short channel device's  $V_T$  and I-V characteristics. This event is known as the hot carrier effect. This problem can be minimised in Lightly Doped Drain (LDD) structure, where most of the drain and source region is heavily doped and the region adjacent to the channel is lightly doped. Therefore, this structure reduces the field between drain and channel; as a result, the hot carrier effect diminishes. The hot electron effect is shown in Fig.1.10.

Fig.1.10: The hot electron effect (D'Agostino & Quercia, 2000)

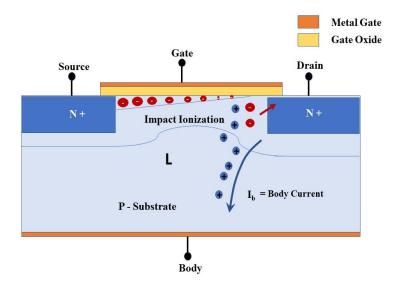

#### **1.2.7 Impact ionisation**

Impact ionisation is the consequence of the hot electron effect. Many electronhole pairs are produced by the impact ionisation of the energetic carriers with the Si atoms. The drain terminal collects the excess amount of electrons. But the holes retain in the body and produce substrate or body current, which is one of the important reasons for the power loss in a short channel device. It also affects the  $g_d$  and holding time of MOS memory device. Fig.1.11 explains the impact ionisation process.

Fig.1.11: Schematic representation of the impact ionisation process (Bhattacharyya, 2009)

#### 1.2.8 Subthreshold swing

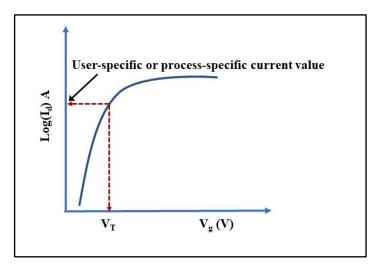

SS that develops as a result of generated electrons in the channel prior to the strong inversion condition is the effect that is made worse by the short channel device. In this condition, these induced electrons diffuse from source to drain, making it hard to switch off the device below the threshold. The DIBL effect exacerbates the subthreshold current. The slope of log of  $I_d$  with  $v_{gs}$  is the measure of SS (Tosaka, Suzuki, & Sugii, 1994). It can be found out by differentiating  $v_{gs}$  with respect to  $\log(I_d)$

$$SS = \frac{dv_{gs}}{d\left(\log I_d\right)} \tag{1.1}$$

A typical  $\log(I_d)$  versus  $v_{gs}$  graph is shown in Fig.1.12. In-room temperature, SS is 60 mV/decade for the ideal transistor. It indicates that the subthreshold current is reduced by one-tenth with the reduction of  $v_g = 60$  mV.

Gate to source voltage

Fig.1.12:  $\log I_d$  Vs  $v_{gs}$  curve (D. Das, 2015)

#### **1.2.9 Quantum mechanical effect**

Quantum mechanical effect (QME) is very important in small geometry devices. As the carrier energy quantisation is triggered due to the structural

|  |  | PAGE NO.    31 |  |

|--|--|----------------|--|

|--|--|----------------|--|

confinement, the energy gap widens and electrons will be in the first sub-band above the conduction band. This results in an increased  $V_T$ .

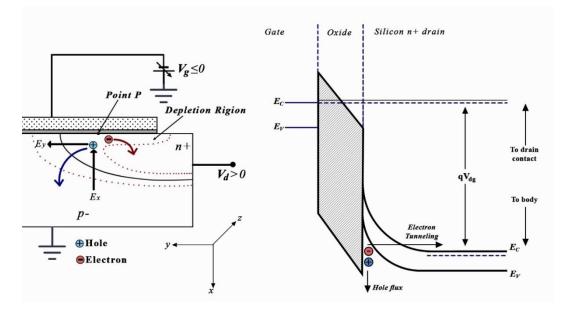

#### 1.2.10 Gate induced drain leakage

Gate induced drain leakage (GIDL) current is materialised due to band-to-band tunnelling mechanism. When drain is linked to a positive bias and the gate is near to zero voltage or a negative voltage, the drain region below the gate is exhausted of free carriers and even it will be inverted under the action of a vertical electric field, as illustrated in Fig.1.13. As the drain is heavily doped, a narrow depletion region and a large electric field is created between the drain and gate. Due to these two-fold effects, electrons tunnel from the valence to the conduction band and are collected by the drain. This kind of leakage current also occurs due to trap assisted tunnelling under low electric field conditions. GIDL contributes significant power loss in a short channel device (Chan, Chen, Ko, & Hu, 1987; Semenov, Pradzynski, & Sachdev, 2002).

Fig.1.13: Graphical representation of GIDL (J.-H. Chen, Wong, & Wang, 2001)

#### 1.2.11 Fringing induced barrier lowering

The gate leakage current can be reduced by replacing  $SiO_2$  with high-k dielectrics. But the higher dielectric materials enhance the equivalent oxide thickness (EOT), which produces a fringing electric field from source to drain, deteriorating the

|  |  | 32 |  |

|--|--|----|--|

|--|--|----|--|

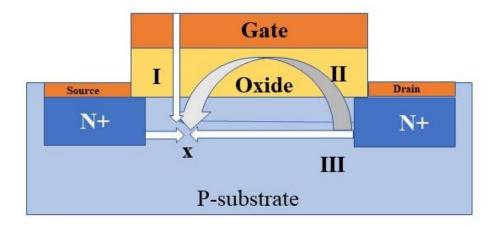

gate control over the channel. This incident is identified as fringe induced barrier lowering (FIBL) (Q. Chen, Wang, & Meindl, 2005; P. Liang, Jiang, & Song, 2008; X. Liu, Kang, Sun, Han, & Wang, 2002).

Fig.1.14 explains the FIBL. The physical distance is the distance measured from point X to the different electrodes. The drain electrode is linked with the channel through path I and path II. It is important to mention that path II coupling can be ignored in long channel devices owing to the small physical width of the gate oxide. But it plays an important role in short channel devices as it is governed by the dielectric gate thickness and the drain-side overlap area. The electrical equivalent distance of path I can be kept constant following the scaling rules. But, the distance between channel and drain decreases in the lateral direction due to improper scaling. Owing to the higher physical thickness of the high-k material, the lines of force decrease at the overlap regions, increasing the fringing effect (Mohapatra, Desai, & Rao, 2003). The increased fringing field is responsible for widening the depletion region beyond the gate in the width direction. Hence, more gate charge is required to create the inversion channel, resulting in enhancement of  $V_T$ .

Fig.1.14: Schematic representation of FIBL (Mohapatra et al., 2003)

#### **1.2.12 Parasitic BJT effect**

The parasitic BJT effect is mainly visible in power MOSFET. In this type of device, the body act as a base. The source and the drain act as emitter and collector,

| PAGE NO.    33    - |  |

|---------------------|--|

|                     |  |

respectively. Normally, the body is shorted with the source to turn off the BJT otherwise, the potential at the body terminal may turn on the BJT and the device will enter into the latch up condition and may damage the device (Baliga, 1996).

#### 1.2.13 Time-dependent dielectric breakdown

Due to the miniaturisation of the semiconductor device, the transverse electric field produces huge stress on the ultra-thin gate oxide. If this device operates under the high electric field for a long time, gate oxide will be degraded and may destroy the device. This phenomenon is known as time-dependent dielectric breakdown (TDDB).

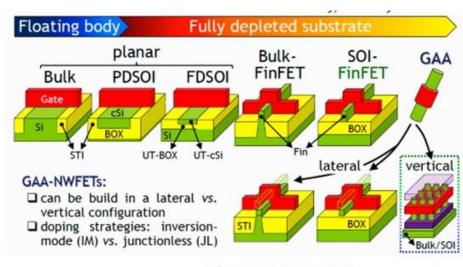

#### **1.3 Multi-gate MOSFET**

Over the past decade, the SOI MOSFET matures from the single gate, planar structure to the multi-gate (MG) structure. While the research on it was started in early 60s (Baliga, 1996; Cobbold & Trofimenkoff, 1964, 1965). The SCEs are more prominent when *L* of CMOS goes down below 100 nm regime. Thermal injection and quantum mechanical (QM) tunnelling lead the device's electrical barriers to drop their insulating characteristics (Yuan Taur et al., 1997). These cause the rapid increase of the chip's standby power, limit the integration level and the switching speed. Therefore, scaling is no more an adequate solution. Processing modules, tools, material qualities, and other factors make scaling a challenging issue. The fabrication process encounters new challenges because of the requirement of new processing steps. Therefore, to address these challenges, it needs a device engineering revolution and a new concept of physics. Hence, the planar MOSFET is transformed into a three dimensional (3-D) MG structure.

The MG arrangement acts as an electrostatic buffer, shielding the channel region from the parasitic field generated by the gate and drain. The absence of transverse field improves  $\mu$ . As *L* goes down, two or more inversion volumes are produced, resulting in a faster carrier movement and high drive current. In a MG structure, the channel is controlled by more than one gate; thereby, lower DIBL and a better *SS* can be achieved. The first fabricated double-gate (DG) SOI MOSFET, fully depleted lean-channel transistor (DELTA, 1989) was constructed on a thin, tall silicon island, generally known as a finger, leg or fin (Hisamoto, Kaga, Kawamoto, & Takeda,

PAGE NO. || 34 ||

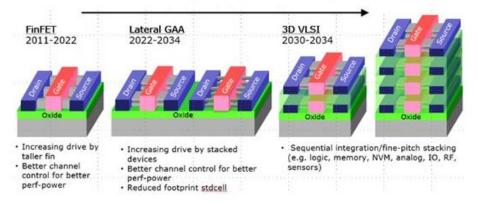

1989). DG, triple-gate (TG) structure such as quantum wire (J.-P. Colinge, Baie, Bayot, & Grivei, 1996), FinFET (Huang et al., 1999) and quadruple structure viz. gate-all-around (GAA) (J.-P. Colinge, Gao, Romano-Rodriguez, Maes, & Claeys, 1990), vertical pillar MOSFETs (C. P. Auth & Plummer, 1998), Pi-gate SOI MOSFETs (Park, Colinge, & Diaz, 2001) are few examples of MG structure. It is important to mention that a single gate probe is placed on opposite sides of the DG device. Following the same technique in TG structure, a single gate electrode is connected to the gate metal, which covers the device from three sides. The multiple independent gate FET (MIGFET) is a notable exception, as two separate gate electrodes are at two unlike potentials. It was reported that if L is below 30 nm, manufacturers must adopt the MG devices to catch up with the International Technology Roadmap for Semiconductors (ITRS) (Association, 2007). Not only the MG structure but vertical scaling is more efficient in the era of the 20<sup>th</sup> century. It was reported that this device will be the most significant architecture that could sustain scaling until 2025 (C. Auth et al., 2017; Veloso et al., 2016; Yeap et al., 2019). The various MG structure is shown in Fig.1.15.

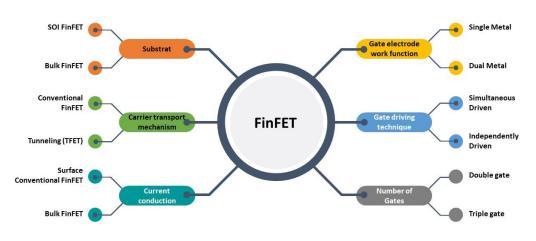

The improved controllability of SCEs and the healthy compatibility with the existing CMOS fabrication technique make the FinFET a potential alternative of CMOS. Generally, FinFET with superior scalability support, undoped or lightly doped channel reduces dopants' random fluctuation (Park & Colinge, 2002; V. Subramanian et al., 2007; S. Xiong & Bokor, 2003; Zhang, Fossum, Mathew, & Du, 2005). The vertical narrow channel which is controlled by more than one gate provides improved electrostatic integrity, that will reduce the scaling of fin body thickness compared to the ultra-thin body and box FD-SOI (UTBB FD-SOI) (Mitard et al., 2014; Xie et al., 2016). Fig.1.16 depicts the classification of FinFET in chart format.

Planar to GAA transition

Fig.1.15: Scaling scenario for device architecture and development of device architecture in the IRDS Roadmap (IEEE, 2020)

Fig.1.16: Classification of FinFET (Lakshmi, 2013)

#### **1.4 Concept of FinFET**

The ongoing increase in integration levels gave rise to FinFET technology. To achieve the enormous gains in integration levels, numerous parameters have been changed. Feature sizes have been decreased to manufacture of more devices in a given space. As process technologies reach 20 nm, it will become impossible to achieve the correct scaling of numerous device parameters since individual device scalability has limits. The supply voltage is the most important aspect in defining dynamic power and it is mainly affected by scaling. Optimising one variable, for example, performance, led to unintended trade-offs in other areas, such as power. As a result, additional options had to be considered. Hence, FinFET comes.

The term FinFET is a generic name. Generally, it denotes any fin-based, MG transistor architecture regardless of gate numbers. Profs. Chenming Hu, Tsu-Jae King-Liu, and Jeffrey Bokor of the University of California, Berkeley were the pioneers of this structure.

The FinFET is a 3-D structure. The vertical fin forms the channel. It also serves as the source and drain, allowing larger volumes in the same area as a standard planar transistor. Therefore, the height of the fin plays a vital role in creating the channel width. The gate is orientated at a right angle and warps the vertical fin. The gate can be viewed as a "multiple" gate surrounding the narrow channel. These MG might exhaust the channel of carriers completely and as a result, better electrostatic control of the channel and improved electrical characteristics can be achieved. The improved electrical characteristics mean the channel can be "choked off" more easily, i.e., nearideal sub-threshold behaviour (related with leakage), which is intricated to attain in the planar technology. One most important feature that makes the transition easier from the planar structure to the vertical structure is that the back-end of the procedure is essentially identical for both, so most of the design flow related to the back-end remains the same.

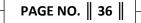

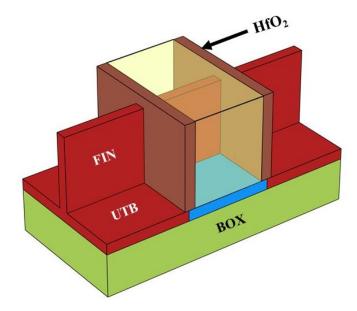

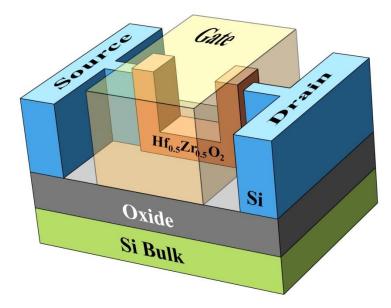

In this research work, a short channel FinFET is considered and depicted in Fig.1.17. The thin fin-shaped silicon (Si) channel is considered on the silicon dioxide (SiO<sub>2</sub>) with a thickness represented by  $t_{oxb}$ . The gate electrode surrounds the fin with the fin height  $(H_{fin})$ , fin width  $(W_{fin})$  and L. The gate oxide thickness  $(t_{ox})$  is

uniform on the three sides of the fin. Thus, the construction forms a TG-FinFET structure.

Fig.1.17: Schematic view of TG-FinFET

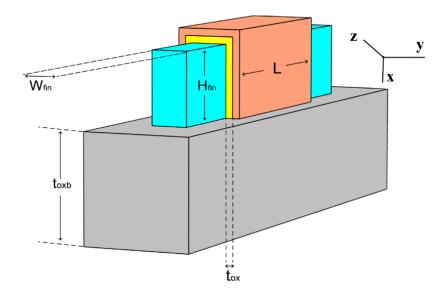

#### **1.5 Need for High-k materials**

With the advancement of semiconductor technology, the size of MOSFETs has been scaled down to sub-100 nm. However, the scalability of individual device parameters has its own limits. The SiO<sub>2</sub> layer with a thickness of 1.2 nm provides a direct tunnelling (DT) current through the gate terminal in the order of 1 A/cm<sup>2</sup> at 1 V. This leads to unacceptable static power dissipation and generates excess heat, which may vandalize the device (Gusev, Narayanan, & Frank, 2006; Ortiz-Conde et al., 2016). Likewise, the fabrication of such thin films is very tough and defective. Thus, SiO<sub>2</sub> had to be replaced.