# INVESTIGATION OF ADIABATIC AND QUASI-ADIABATIC LOGIC TECHNIQUES FOR DIGITAL CMOS CIRCUITS

# A THESIS SUBMITTED IN PARTIAL FULLFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILLOSHOPHY

#### REGINALD H. VANLALCHAKA

**MZU REGN NO: 1800061**

Ph.D. REGN NO: MZU/Ph.D./1293 of 03.08.2018

# DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING

SCHOOL OF ENGINEERING AND TECHNOLOGY

**JULY 2025**

## INVESTIGATION OF ADIABATIC AND QUASI-ADIABATIC LOGIC TECHNIQUES FOR DIGITAL CMOS CIRCUITS

#### BY

#### REGINALD H. VANLALCHAKA

Department of Electronics & Communication Engineering

Name of Supervisor: Prof. NILADRI PRATAP MAITY

Joint- Supervisor: Prof. RESHMI MAITY

#### Submitted

In partial fulfillment of the requirement of the Degree of Doctor of Philosophy in Electronics & Communication Engineering of Mizoram University, Aizawl

**Department of Electronics And Communication Engineering**

School of Engineering And Technology

MIZORAM UNIVERSITY

(A Central University)

Tanhril, Aizawl – 796 004, Mizoram

**CERTIFICATE**

This is to certify that the thesis entitled "Investigation of Adiabatic and Quasi-Adiabatic

Logic Techniques for Digital CMOS Circuits" submitted to Mizoram University for the

award of the degree of Doctor of Philosophy in Electronics and Communication Engineering

Reginald H. Vanlalchaka, Ph.D. Registration No. MZU/Ph.D./1293 of 03.08.2018, is Ph.D.

scholar in the Department of Electronics and Communication, under my guidance and

supervision and has not been previously submitted for the award of any degree in any Indian or

foreign University. He has fulfilled all criteria prescribed by the UGC (Minimum Standard and

Procedure governing Ph.D. Regulations). He has fulfilled the mandatory publication (Publication

enclosed) and completed Ph.D. course work. It is also certified that the scholar has been admitted

in the Department through an entrance test, followed by an interview as per UGC Regulation of

2016.

Date: October, 2024

Place: Aizawl

(Prof. NILADRI PRATAP MAITY)

Supervisor

(Prof. RESHMI MAITY)

Joint-Supervisor

1

**DECLARATION**

**MIZORAM UNIVERSITY**

**JULY 2025**

I Reginald H. Vanlalchaka, hereby declare that the subject matter of this thesis is the record

of work done by me, that the contents of this thesis did not form basis of the award of any

previous degree to me or to do the best of my knowledge to anybody else, and that the thesis has

not been submitted by me for any research degree in any other University/Institute.

This is being submitted to the Mizoram University for the Degree of Doctor of Philosophy in

**Electronics and Communication Engineering.**

Date: (REGINALD H. VANLALCHAKA)

Candidate

(Prof. NILADRI PRATAP MAITY)

**Supervisor**

(Prof. P.V. NAGANJANEYULU)

(Prof. RESHMI MAITY)

**Head of Department Electronics and Communication Engineering**

**Joint-Supervisor**

### Acknowledgement

First and foremost, I am deeply thankful to the **Almighty God** for bestowing upon me wisdom, health, and apportionment throughout the course of this research. His blessings have guided and sustained me. I express my profound gratitude to my supervisor, Prof. Niladri Pratap Maity, for his expert guidance and directions. His support and insights have been crucial in the development of this thesis. I sincerely thank **Prof. Reshmi Maity**, Head of the ECE Department, for granting me access to the department's laboratory and resources. Her cooperation has been instrumental in the advancement of my research. I am immensely grateful to my parents for their moral support, encouragement, and prayers. Their unwavering belief in me has been my greatest source of strength and motivation. Special thanks are due to my dear sister, **Dr. Vanlalruatkimi**, for her assistance in thesis writing and editing. Her contributions have been invaluable to refining this thesis. I extend my deepest appreciation to my wife, J. Vanlalhriatpuii, for her constant encouragement and understanding. Her support has been a cornerstone of my perseverance. I also wish to acknowledge my eldest brother, Dr. Vanlalhmuliana, for his inspiration and financial support. His contributions have been vital to my academic journey. I am deeply thankful to my family for their unwavering support, which has been a source of immense comfort and motivation. I would like to express my gratitude to Dr. Lalthanpuii Khiangte for her assistance with the software I acquired, which has played a significant role in my research.

Lastly, I extend my thanks to the teaching and non-teaching staff of the ECE Department, MZU, for their assistance and cooperation. Your dedication has greatly contributed to the completion of this thesis. I also appreciate any other individuals who have provided direct or indirect assistance throughout this journey.

(REGINALD H. VANLALCHAKA)

| Chapter – 1: Introduction                                 | 1-25                  |

|-----------------------------------------------------------|-----------------------|

| 1.1. Background                                           | 1                     |

| 1.1.1. Small-Scale Integration (SSI)                      | 1                     |

| 1.1.2. Medium-Scale Integration (MSI)                     | 1                     |

| 1.1.3. Large-Scale Integration (LSI)                      | 2                     |

| 1.1.4. Very Large-Scale Integration (VLSI)                | 2                     |

| 1.1.5. Ultra-Large-Scale Integration (ULSI)               | 2                     |

| 1.2. Problem Description                                  | 2<br>2<br>2<br>3<br>4 |

| 1.3. Motivation                                           | 4                     |

| 1.4. Lower Power-Design Method                            | 4                     |

| 1.4.1. System Level Design                                | 5                     |

| 1.4.2. Algorithm Level Design                             | 5                     |

| 1.4.3. Architecture Level Design                          | 6                     |

| 1.4.4. Circuit Level Design                               | 6                     |

| 1.4.5. Device Level Design                                | 6                     |

| 1.5. Different Power Consumptions in Digital CMOS Circuit | 7                     |

| 1.5.1. Dynamic Power Consumption                          | 7                     |

| 1.5.1.1. Switching Power Consumption                      | 8                     |

| 1.5.1.2. Short Circuit Power Consumption                  | 11<br>12              |

| 1.5.1.3. Glitching Power Consumption                      | 12                    |

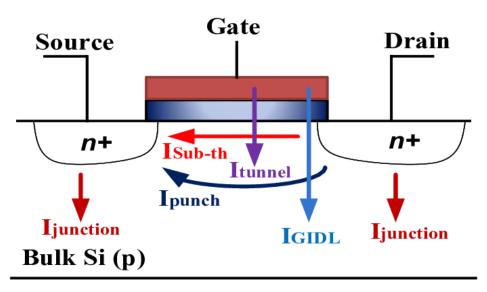

| 1.5.2. Static Power Consumption 1.5.2.1. Leakage Currents | 14                    |

| 1.5.2.2. Sub-Threshold or weal inversion currents         | 15                    |

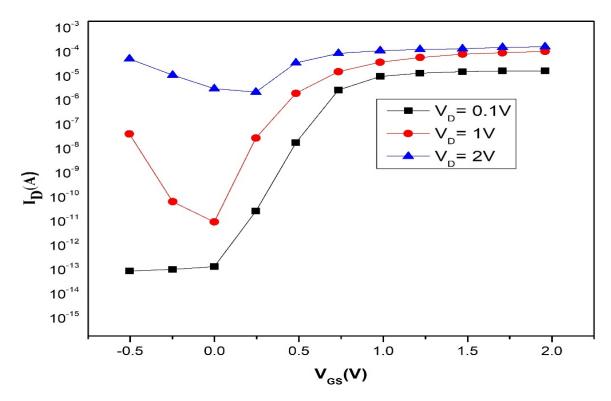

| 1.5.2.3. Gate-Induced Drained Leakage                     | 16                    |

| 1.5.2.4. Punch-Through Current                            | 18                    |

| 1.5.2.5. Gate Tunneling Current                           | 20                    |

| 1.5.2.6. Junction Leakage                                 | 21                    |

| 1.6. Reduction of Power Consumption                       | 21                    |

| 1.6.1. Voltage Scaling                                    | 22                    |

| 1.6.2. Clock Gating                                       | 22                    |

| 1.6.3. Multi-Vt. (Threshold Voltage) Design               | 22                    |

| 1.6.4. Power Gating                                       | 23                    |

| 1.6.5. Static/Leakage Power Dissipation Reduction         | 23                    |

| 1.6.6. Reverse Body Biasing                               | 23                    |

| 1.6.7. Leakage Control Cell                               | 23                    |

| 1.6.8. Sub-Threshold Logic                                | 23                    |

| 1.7.Thesis Organization                                   | 24                    |

| 1.7.1 hesis Organization                                  | 2.                    |

| Chapter – 2: Review Literature                            | 26 -64                |

| 2.1. Introduction to Adiabatic Logic                      | 26                    |

| 2.2. The Charging Process in Adiabatic Logic              | 26                    |

| 2.3. A Review of Adiabatic Logic Family                   | 29                    |

| 2.3.1. Hot Clock NMOS                                     | 30                    |

|                                                           |                       |

| 2.3.2. Recovered Energy Logic (REL                        | 31                    |

| 2.3.3. Split-Level Charge Recovery Logic (SCRL)           | 32                    |

**CHAPTER AND TITLE**

**PAGE**

| 2.3.4. 2N 2N2D                                                    | 33       |

|-------------------------------------------------------------------|----------|

| 2.3.5. Adiabatic Dynamic Logic (ADL)<br>2.3.6. 2N 2N2P            | 33<br>34 |

| 2.3.7. Efficient Charge Recovery Logic (ECRL)                     | 35       |

| 2.3.8. Adiabatic Pseudo-domino logic (APDL)                       | 36       |

| 2.3.9. Clocked CMOS Adiabatic Logic (CAL)                         | 36       |

| 2.3.10. Positive Feedback Adiabatic Logic (PFAL)                  | 37       |

| 2.3.11. Energy Efficient Logic (EEL)                              | 38       |

| 2.3.12. Pass-transistor Adiabatic Logic (PAL)                     | 39       |

| 2.3.13. Improved Adiabatic Pseudo-Domino Logic (IAPDL)            | 40       |

| 2.3.14. Improved Efficient Charge Recovery Logic (IECRL)          | 41       |

| 2.3.15. Reversible Energy Recovery Logic (RERL)                   | 42       |

| 2.3.16. True Single-Phase Energy Recovery Logic (TSEL)            | 42       |

| 2.3.17. Source Coupled Adiabatic Logic (SCAL)                     | 43       |

| 2.3.18. NMOS Energy Recovery Logic (NERL)                         | 44       |

| 2.3.19. High-Efficient Energy Recovery Logic (HEERL               | 45       |

| 2.3.20. Improved Pass-Gate Adiabatic Charge Recovery Logic (IPGL) | 46       |

| 2.3.21. Improved Pass-Gate Adiabatic Charge Recovery Logic (IPGL) | 47       |

| 2.3.22. Complementary Pass-Transistor Adiabatic Logic (CPAL)      | 47       |

| 2.3.23. Dual Transmission Gate Adiabatic Logic (DTGAL)            | 48       |

| 2.3.24. 2N-2N2P2D Logic                                           | 49       |

| 2.3.25. Quasi-Static Single-phase Energy Recovery Logic (QSSERL)  | 50       |

| 2.3.26. Clocked Transmission Gate Adiabatic Logic (CTGAL)         | 50       |

| 2.3.27. Glitch-Free and Cascadable Adiabatic Logic (GFCAL)        | 51       |

| 2.3.28. Two-Phase Clocked CMOS Adiabatic Logic (2PC2AL)           | 52       |

| 2.3.29. Improved Clocked Adiabatic Logic (ICAL)                   | 53       |

| 2.3.30. Energy-Efficient Adiabatic Logic (EFAL)                   | 53       |

| 2.3.31. Pre-resolve and Sense Adiabatic Logic (PSAL)              | 55       |

| 2.3.32. Secured Quasi Adiabatic Logic (SQAL)                      | 55       |

| 2.3.33. Symmetric Pass Gate Adiabatic Logic (SPGAL)               | 55       |

| 2.4. Power Supply in Adiabatic Logic                              | 61       |

| 2.4.1. Mathematical Design of an Adiabatic Power Supply           | 63       |

| Chapter -3: Improved Diode Free Adiabatic Logic                   | 65-93    |

| 3.1. Introduction                                                 | 65       |

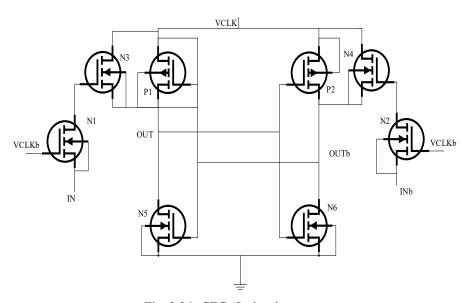

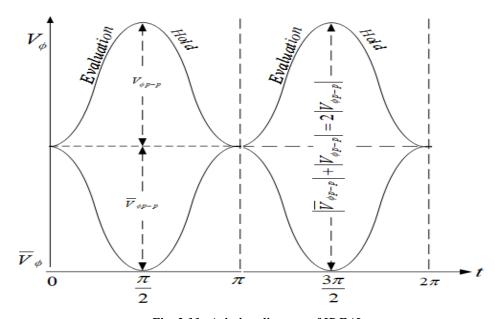

| 3.1.1. Description of Power Clock                                 | 66       |

| 3.2. Adiabatic Logic Families Involved in the Work                | 67       |

|                                                                   |          |

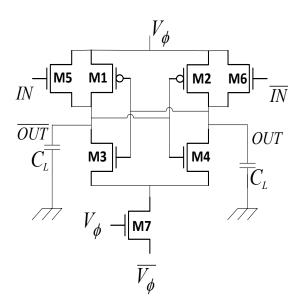

| 3.3. Structure of Improved Diode Free Adiabatic Logic (IDFAL) | 69      |

|---------------------------------------------------------------|---------|

| 3.3.1. Working of the Circuit                                 | 71      |

| 3.3.2. Dynamic Energy Consumption                             | 72      |

| 3.3.3. Leakage Energy Consumption                             | 75      |

| 3.4. Circuit Using IDFAL                                      | 76      |

| 3.4.1. Basic Inverter Circuit                                 | 77      |

| 3.4.2. NAND Gate Using IDFAL                                  | 79      |

| 3.4.3. IDFAL Inverter Chain                                   | 80      |

| 3.4.4. SR Flip Flop Using IDFAL                               | 82      |

| 3.5. Results And Discussion                                   | 83      |

| 3.6. Summary                                                  | 93      |

| Chapter – 4: Sequential and Combinational Circuits            | 94-129  |

| With Improved Diode Free Adiabatic Logic (IDFAL)              |         |

| 4.1. Introduction                                             | 94      |

| 4.2. Work Involving Adiabatic Logic Families                  | 95      |

| 4.3. Analysing the IDFAL Circuit                              | 98      |

| 4.3.1. Simulation of Basic IDFAL Inverter Circuit             | 99      |

| 4.4. The IDFAL Sequential Circuits                            | 101     |

| 4.4.1. SR Flip Flop Using IDFAL                               | 102     |

| 4.4.2. D Flip Flop Using IDFAL                                | 104     |

| 4.4.3. T Flip Flop Using IDFAL                                | 107     |

| 4.5. The IDFAL Combinational Circuit                          | 110     |

| 4.5.1. Full Adder Using IDFAL                                 | 111     |

| 4.5.2. Single Bit Comparator Using IDFAL                      | 114     |

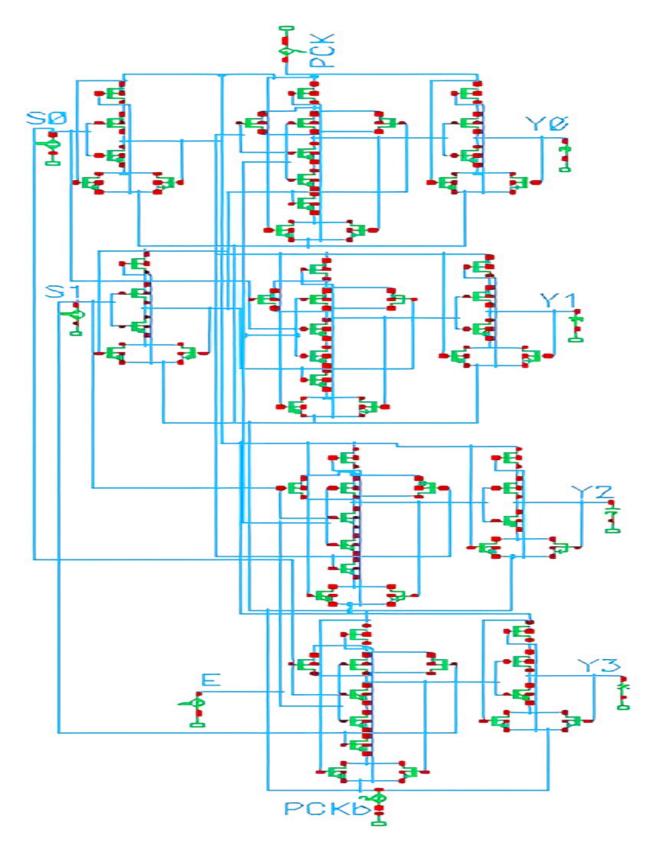

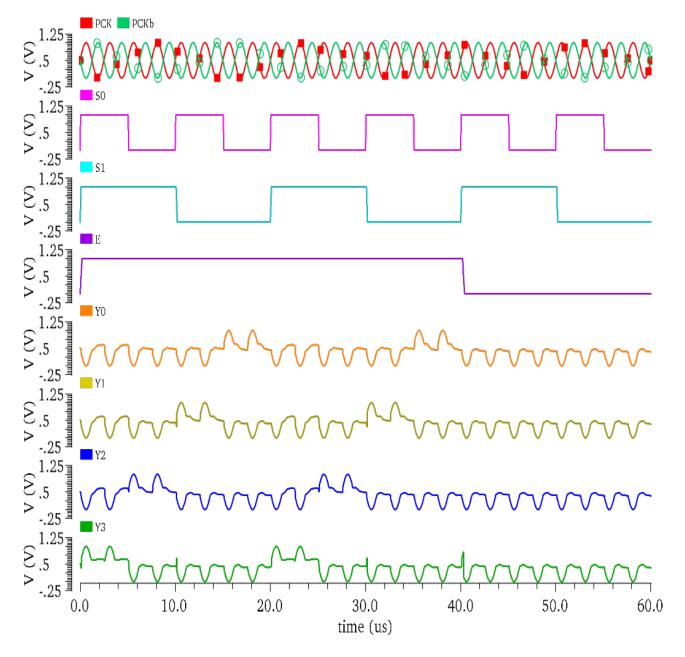

| 4.5.3. 2x4 Decoder Using IDFAL                                | 117     |

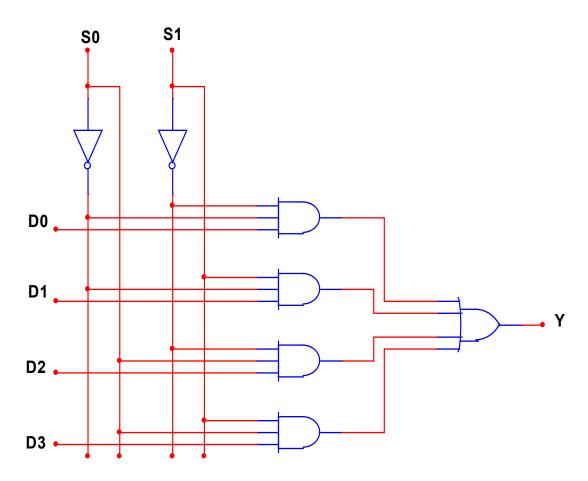

| 4.5.4. 4x1 Multiplexer Using IDFAL                            | 121     |

| 4.6. Results And Discussions                                  | 125     |

| 4.6.1. Comparisons of Various Result in The Table             | 127     |

| 4.7. Summary                                                  | 129     |

| CHAPTER – 5: A Low Power Design Using FinFET                  | 130-147 |

| Based Adiabatic Switching Principle: Application              |         |

| to 16-Bit Arithmetic Logic Unit                               |         |

| 5.1. Introduction                                             | 130     |

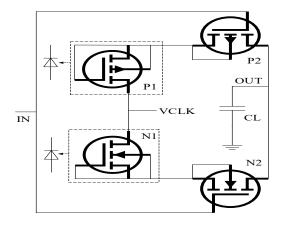

| 5.2. Proposed Method                                          | 131     |

| 5.3. Proposed Circuit                                                                            | 133        |

|--------------------------------------------------------------------------------------------------|------------|

| <ul><li>5.4. Arithmetic Logic Unit Design Approach</li><li>5.5. Results And Discussion</li></ul> | 139<br>143 |

|                                                                                                  | 143        |

| 5.6. Summary                                                                                     | 140        |

| Chapter – 6: Efficient Low-Power Circuits With                                                   | 147-184    |

| Enhanced Positive Feedback Adiabatic Logic                                                       |            |

| (EPFAL)                                                                                          |            |

| 6.1. Introduction                                                                                | 147        |

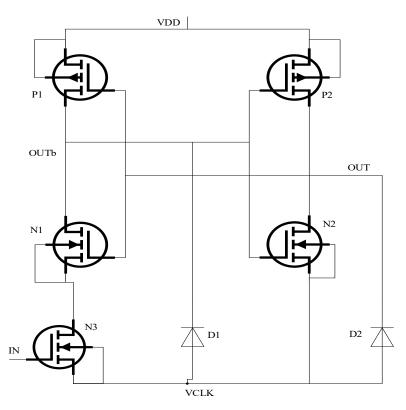

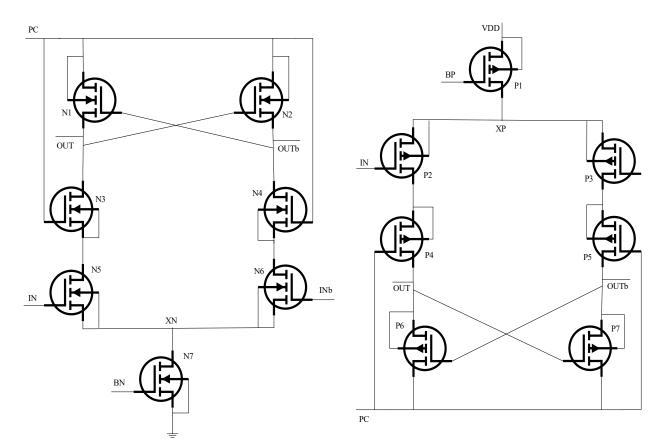

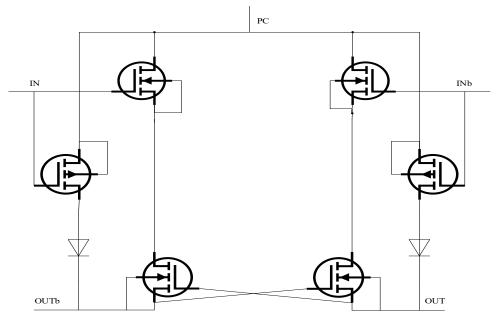

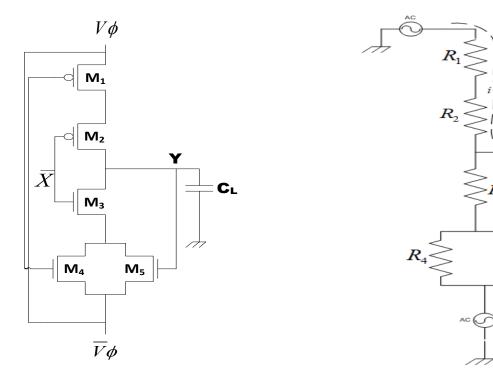

| 6.2. Structure of the Circuit                                                                    | 148        |

| 6.3. Mathematical Analysis                                                                       | 149        |

| 6.4. Adiabatic Logic Family Employed in The Work                                                 | 152        |

| 6.5. Circuits Simulations                                                                        | 155        |

| 6.6. The Parity Circuits                                                                         | 163        |

| 6.6.1. The Parity Generator                                                                      | 164        |

| 6.6.1.1. Even Parity Checker                                                                     | 164        |

| 6.6.1.2. Odd Parity Generator                                                                    | 167        |

| 6.6.2. The Parity Checker                                                                        | 171        |

| 6.6.2.1. Even Parity Checker                                                                     | 171        |

| 6.6.2.2. Odd Parity Checker                                                                      | 175        |

| 6.7. Results And Discussion                                                                      | 179        |

| 6.8. Summary                                                                                     | 182        |

| Chapter – 7: A Power Efficient Fully Adiabatic Logic                                             | 184-207    |

| Circuit Design Approach: Application to Inverter                                                 |            |

| and 8421 Code to Excess- 3 Code Converter                                                        |            |

| 7.1 Introduction                                                                                 | 184        |

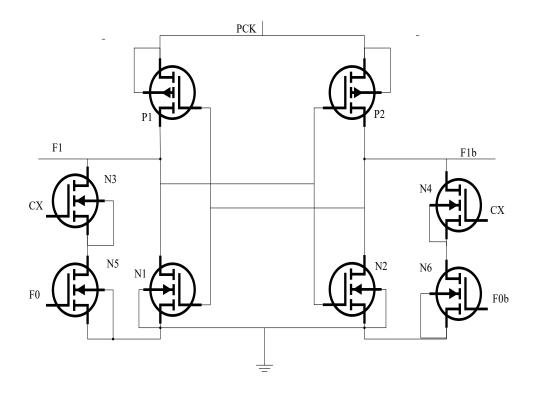

| 7.2. Proposed Inverter Logic                                                                     | 188        |

| 7.3. Average Power Consumption Analyses with Predictive Technologies                             | 192        |

| 7.4. BCD To Excess-3 Converter Circuit Based on Proposed Logic                                   | 195        |

| 7.5. Results And Discussion                                                                      | 198        |

| 7.6. Summary                                                                                     | 206        |

| Chapter– 8: Conclusion and Future Scope                                                          | 207-209    |

| 8.1. Introduction                                                                                | 207        |

| 8.2. Future Scope                                                                                | 208        |

| LIST OF TABLES                                                                                                                                                                                          | PAGE |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Table 1.1: Truth Table of XOR- gate                                                                                                                                                                     | 11   |

| Table 2.1: The Efficiency of Three Popular Charging Waveforms                                                                                                                                           | 63   |

| <b>Table 3.1:</b> Different CMOS technology notes, their respective power supply, parameter and aspect ration                                                                                           | 84   |

| <b>Table 3.2:</b> Comparison of 180 nm TSMC Inverter Power Consumption at Various Operating Frequency Within Four Clock Periods or Cycle Times of Their Respective Inputs                               | 85   |

| <b>Table 3.3:</b> Leakage Current and Leakage Power Measurements Within 40 nm Simulation Time, at a Frequency of 100 MHz                                                                                | 85   |

| <b>Table 3.4:</b> Comparison of 45nm_HP_PTM Inverter Circuits' Power Consumptions at Several Operating Frequencies Within Four Clock Periods or Cycle Times of Their Respective Inputs                  | 86   |

| <b>Table 3.5:</b> Comparison of 32nm_HP_PTM Inverter Circuits' Power Consumptions at Various Operating Frequency Within Four Clock Periods or Cycle Times of Their Respective Inputs                    | 86   |

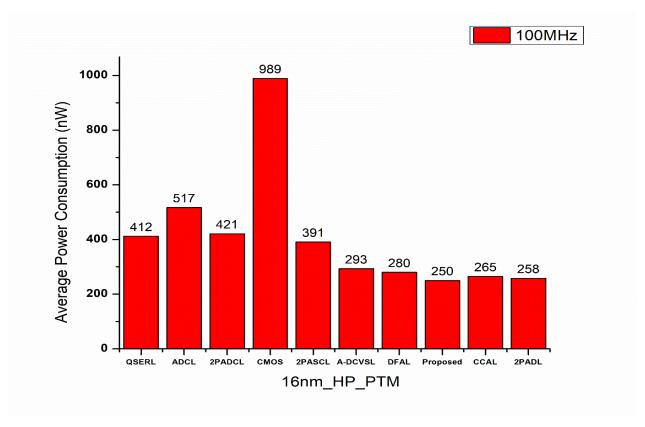

| <b>Table 3.6:</b> 16nm_HP_PTM: Performance Comparison of Basic Gates Designed Using Conventional CMOS and Various Adiabatic Logic Techniques Within 40nm Simulation Time at 100 MHz operating frequency | 87   |

| <b>Table 3.7:</b> 22nm_HP_PTM: Performance Comparison of Basic Gates Designed Using Conventional CMOS and Various Adiabatic Logic Techniques Within 40nm Simulation Time at 100 MHz operating frequency | 88   |

| <b>Table 3.8:</b> 32nm_HP_PTM: Performance Comparison of Basic Gates Designed Using Conventional CMOS and Various Adiabatic Logic Techniques Within 40nm Simulation Time at 100 MHz operating frequency | 89   |

| <b>Table 3.9:</b> 45nm_HP_PTM: Performance Comparison of Basic Gates Designed Using Conventional CMOS and Various Adiabatic Logic Techniques Within 40nm Simulation Time at 100 MHz operating frequency | 90   |

| <b>Table 3.10:</b> Comparison of Average Power Consumption of Basic Gates, Designed Using IDFAL at Various Technology Nodes                                                                             | 91   |

| Table 4.1: Truth table of an SR Flip-Flop                                                                                                                                                               | 102  |

| <b>Table 4.2:</b> Truth table of D a Flip-Flop                                                                                                                                                          | 105  |

| Table 4.3: Truth table of a T Flip-Flop                                                                                                                                                                 | 107  |

| Table 4.4: Truth table of a full adder                                                                                                                                                                                                                 | 111 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 4.5: Truth table of a I-Bit comparator                                                                                                                                                                                                           | 114 |

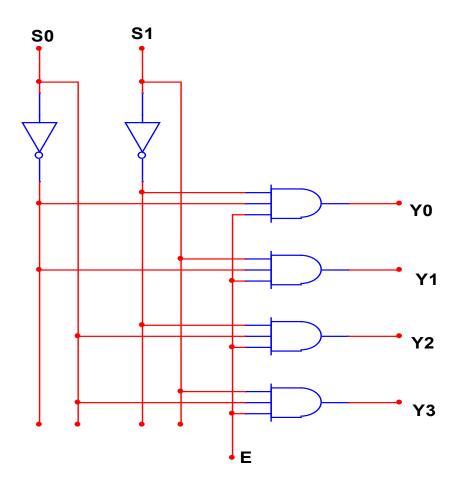

| Table 4.6: Truth table of a 2X4 decoder                                                                                                                                                                                                                | 118 |

| <b>Table 4.7:</b> Truth table of a 4x1 multiplier                                                                                                                                                                                                      | 121 |

| Table 4.8: 45nm_LP_PTM; Performance Comparisons of Various Sequential Circuits Using Conventional CMOS and Several Adiabatic Logic Design Techniques Within 40μm Simulation Time at 100KHz Operating Frequency                                         | 127 |

| <b>Table 4.9:</b> 45nm_LP_PTM; Performance Comparisons of Various Combinational Circuits Using Conventional CMOS and Several Adiabatic Logic Design Techniques Within 40μ Simulation Time at 100KHz Operating Frequency                                | 128 |

| Table 5.1: Truth table of Basic 1-Bit ALU                                                                                                                                                                                                              | 143 |

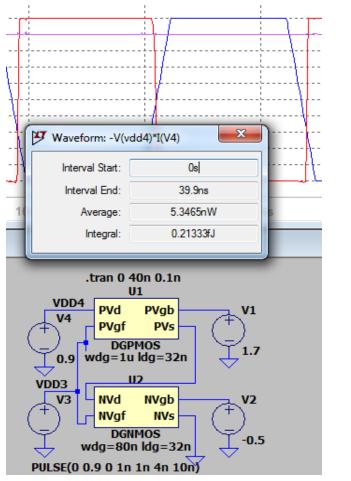

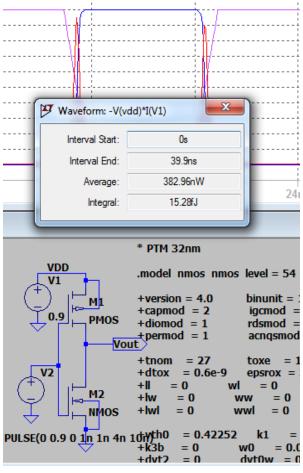

| <b>Table 5.2:</b> Performance of different logic style for 16-bit ALU (MOSFET)                                                                                                                                                                         | 145 |

| <b>Table 5.3:</b> Performance of various logic technique for 16-bit ALU (FINFET)                                                                                                                                                                       | 145 |

| <b>Table 5.4:</b> Power saving (in %) for proposed logic (MOSFET) at 500MH <sub>Z</sub>                                                                                                                                                                | 146 |

| <b>Table 5.5:</b> Power saving (in %) for proposed logic (FinFET) at 500MH <sub>Z</sub>                                                                                                                                                                | 146 |

| Table 5.6: Power saving (in %) from MOSFET TO FinFET                                                                                                                                                                                                   | 146 |

| <b>Table 6.1:</b> Truth table of three bit even parity generator                                                                                                                                                                                       | 164 |

| <b>Table 6.2:</b> Truth table of three bit odd parity generator                                                                                                                                                                                        | 168 |

| <b>Table 6.3:</b> Truth table of four bit received even parity checker                                                                                                                                                                                 | 171 |

| Table 6.4: Truth table of four bit received odd parity checker                                                                                                                                                                                         | 175 |

| <b>Table 6.5:</b> Comparison of 45nm-LP-PTM inverter circuits' power consumption (in nano watts) at several operational frequencies within five clock periods or cycle time of their respective inputs                                                 | 179 |

| <b>Table 6.6:</b> 45nm_LP_PTM; Comparison of Average Dynamic Power Consumption (in Nano Watts) for Basic Gates Designed using conventional CMOS and various adiabatic logic techniques. Within 100 m of simulation time at 100 kHz operating frequency | 180 |

| <b>Table 6.7:</b> 45nm_LP_PTM: Average Dynamic Power Consumption (in Nano Watts) for Basic Gates Designed Using Conventional CMOS Within 100μm Simulation Time at 100KHz Operating Frequency                                                           | 181 |

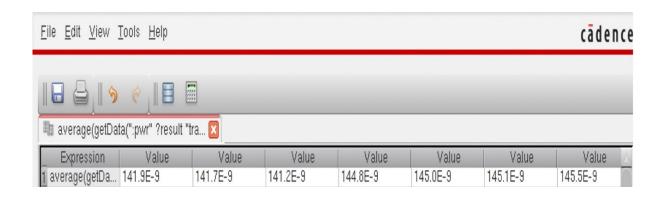

| <b>Table 7.1:</b> Comparison of 45nm_HP_PTM Inverter Circuits' Power Consumptions at Several Operating Frequencies Within Five Clock Periods or Cycle Times of Their Respective Input                                                                  | 193 |

| 194 |

|-----|

| 196 |

| 205 |

| 205 |

| 205 |

|     |

| Fig. 1.1: Moore Law number of transistors per device: past, present, future        | 3  |

|------------------------------------------------------------------------------------|----|

| Fig.1.2: Low power design methodology                                              | 5  |

| Fig.1.3: Classification of various power consumptions in CMOS circuit              | 7  |

| Fig.1.4: CMOS inverter (a) Charging from VDD to CL (b) Dis-Charging from CL to GND | 8  |

| Fig.1.5: Graphical representation of short circuit path in CMOS inverter           | 12 |

| Fig.1.6: Transition of signals through logic gates                                 | 13 |

| Fig 1.7: Reduction of glitching using gates                                        | 13 |

| Fig.1.8: Leakage currents in a MOSFET                                              | 15 |

| Fig.1.9: Gate-source voltage vs. drain current                                     | 17 |

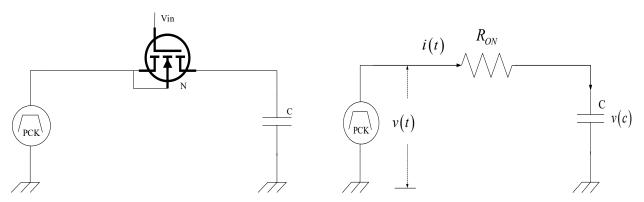

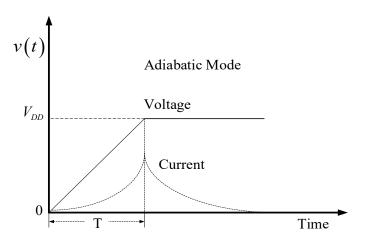

| Fig.2.1: Adiabatic switching model                                                 | 27 |

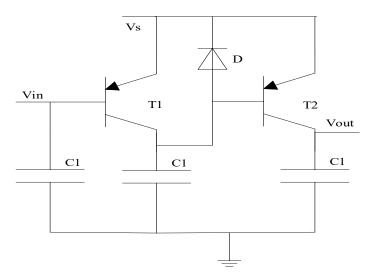

| Fig 2.2: Recovery energy logic (REL) inverter                                      | 31 |

| Fig.2.3: Split level charge recovery logic (SCRL)                                  | 32 |

| Fig. 2.4: 2N-2N2D inverter                                                         | 33 |

| Fig. 2.5: Adiabatic dynamic logic (ADL)inverter                                    | 34 |

| Fig.2.6: 2N-2N2P inverter                                                          | 34 |

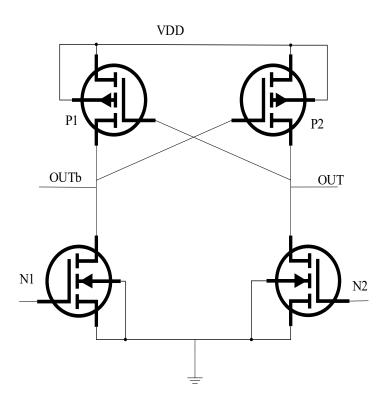

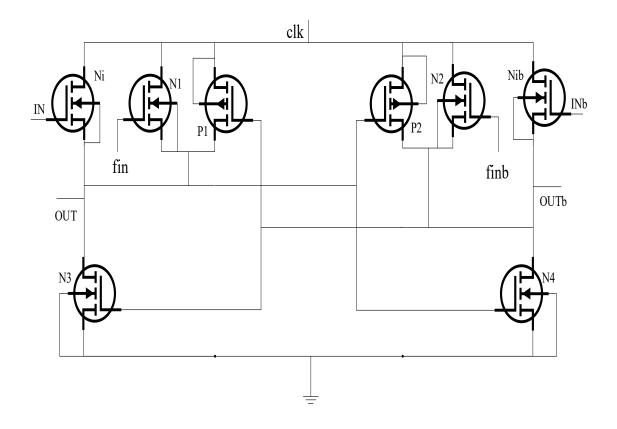

| Fig.2.7: Efficient charge recovery logic (ECRL) inverter                           | 35 |

| Fig. 2.8: Adiabatic pseudo domino logic (APDL)                                     | 36 |

| Fig.2.9: CAL inverter                                                              | 37 |

| Fig.2.10: PFAL inverter                                                            | 38 |

| Fig.2.11: Energy efficient logic (EEL)                                             | 39 |

| Fig.2.12: Implementation of Q=A.B+C in PAL                                         | 40 |

| Fig.2.13: IAPDL Buffer                                                             | 40 |

| Fig.2.14: IECRL inverter                                                           | 41 |

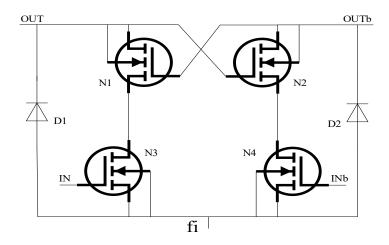

| Fig.2.15: RERL inverter                                                            | 42 |

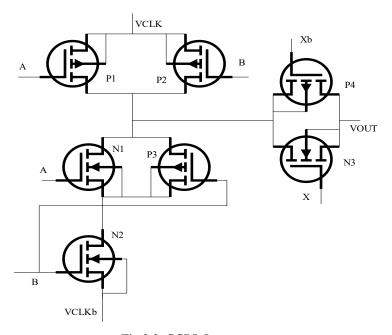

| Fig.2.16: TSEL NMOS inverter                                                       | 43 |

| Fig.2.17: TSEL PMOS inverter                                                       | 43 |

| Fig.2.18: (a) SCAL NMOS inverter (b) SCAL PMOS inverter                            | 44 |

| Fig.2.19: NERL inverter                                                            | 45 |

| Fig.2.20: HEERL inverter                                                           | 45 |

**LIST OF FIGURES**

**PAGE**

| Fig.2.21: IAPDL-2 inverter                                                         | 46       |

|------------------------------------------------------------------------------------|----------|

| Fig.2.22: CPAL inverter Fig.2.23: DTGAL inverter                                   | 47<br>48 |

| Fig.2.24: 2N-2N2P2D inverter                                                       | 49       |

| Fig.2.25: QSSERL inverter                                                          | 49       |

| Fig.2.26: CTGAL circuit                                                            | 50       |

| Fig.2.27: GFGAL inverter                                                           | 51       |

| Fig.2.28: 2PC2AL inverter                                                          | 51       |

| Fig.2.29: ICAL inverter/Buffer                                                     | 52       |

| Fig.2:30: EEAL inverter                                                            | 53       |

| Fig.2.31: PSAL inverter                                                            | 54       |

| Fig.2.32: SQAL inverter                                                            | 55       |

| Fig.2.33: SPGAL inverter                                                           | 56       |

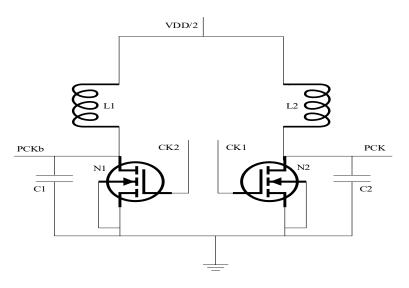

| Fig.2.34: Synchronous two-phase power clock generator                              | 61       |

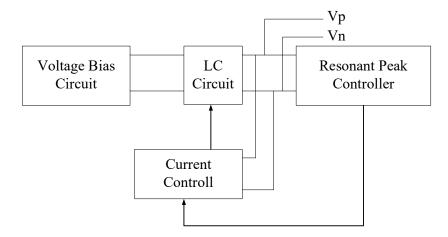

| Fig. 2.35: Block diagram of LC resonant based supply circuit for adiabatic circuit | 62       |

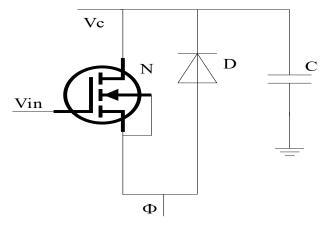

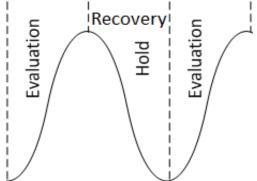

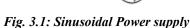

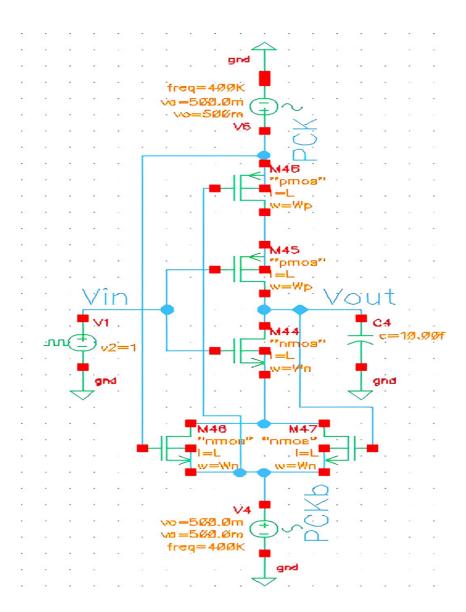

| Fig.3.1: Sinusoidal power supply                                                   | 67       |

| Fig.3.2: Trapezoidal power supply                                                  | 67       |

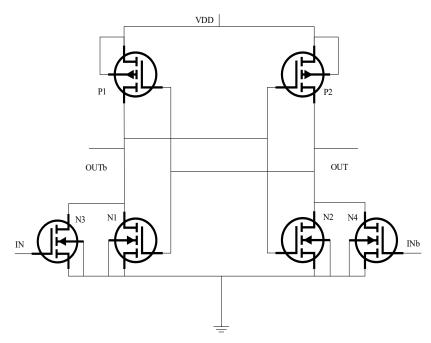

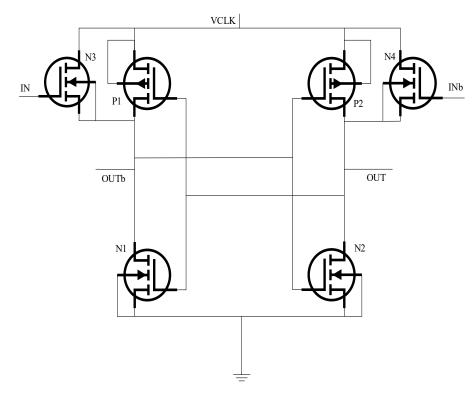

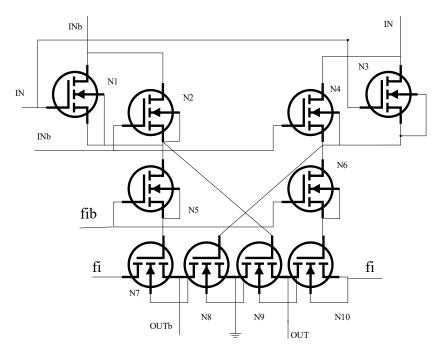

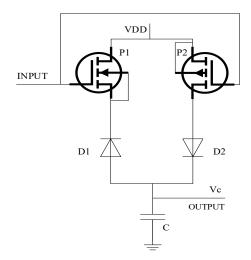

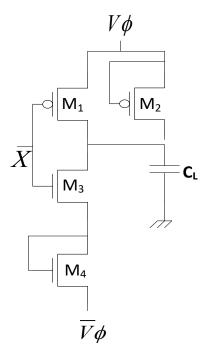

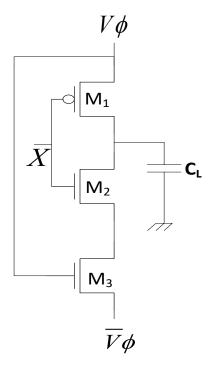

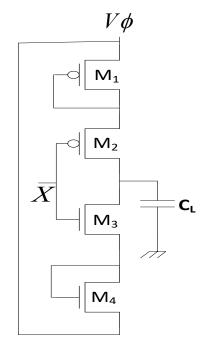

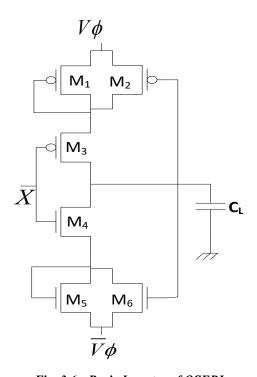

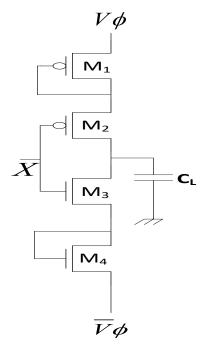

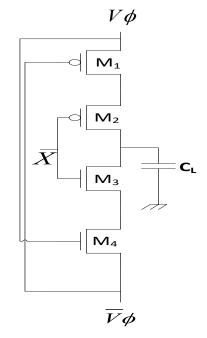

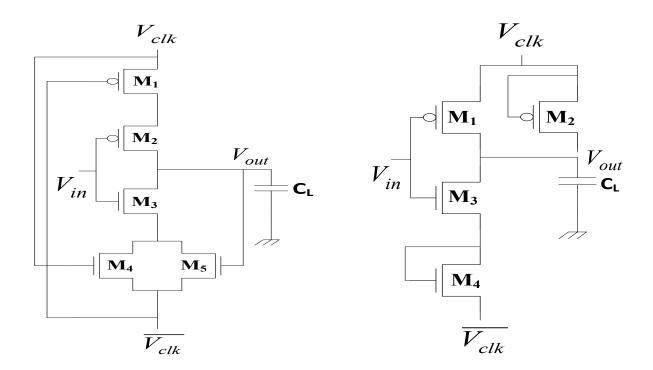

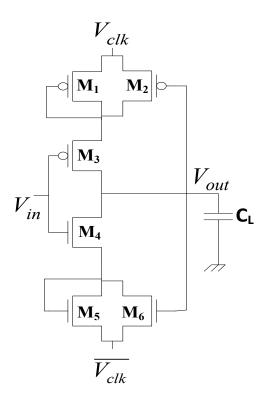

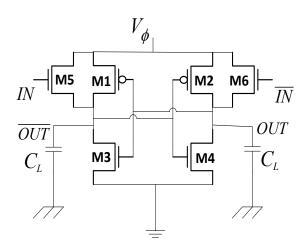

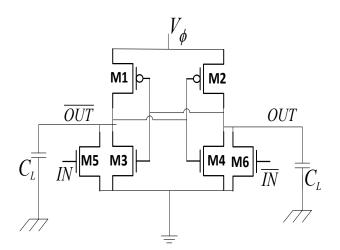

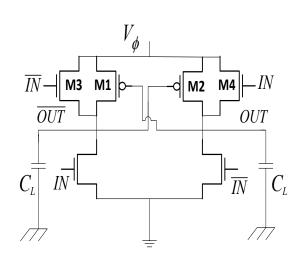

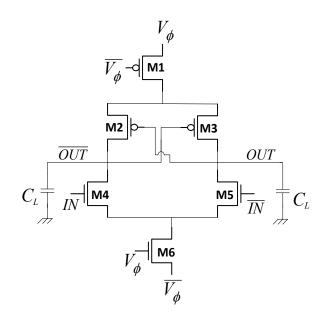

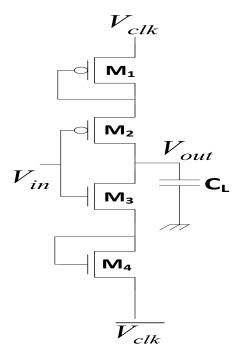

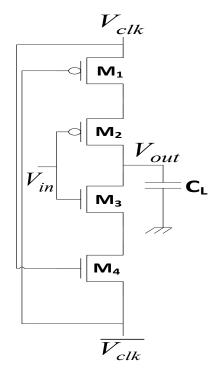

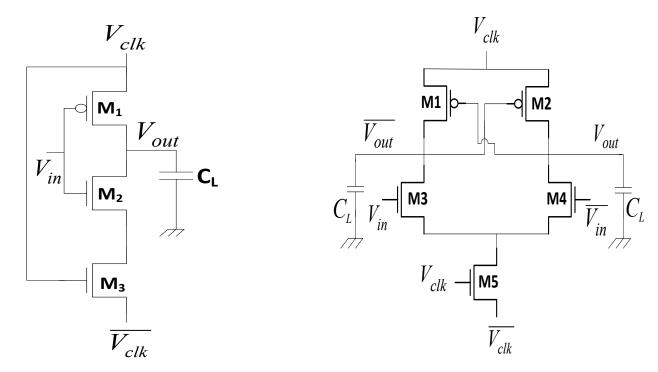

| Fig.3.3: Basic inverter of 2PASCL                                                  | 68       |

| Fig.3.4: Basic inverter of ADCL                                                    | 68       |

| Fig.3.5: Basic inverter of DFAL                                                    | 68       |

| Fig.3.6: Basic inverter of QSERL                                                   | 68       |

| Fig.3.7: Basic inverter of 2PADCL                                                  | 69       |

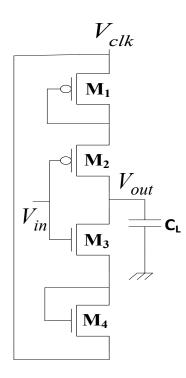

| Fig.3.8: Basic inverter of CCAL                                                    | 69       |

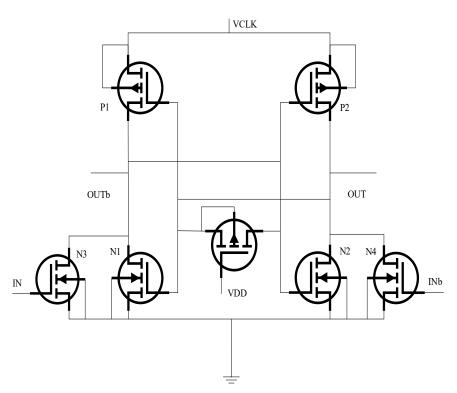

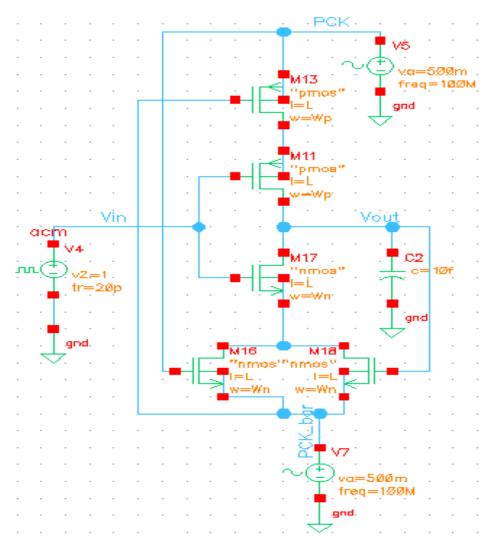

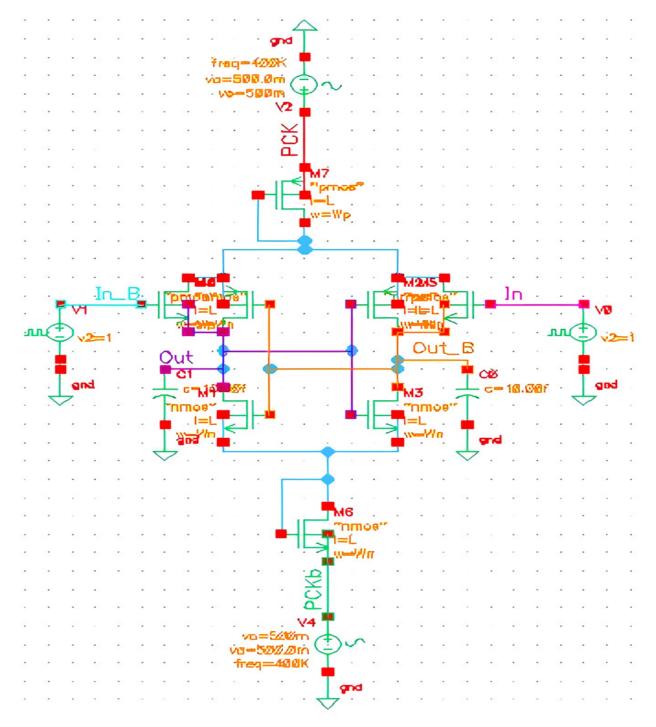

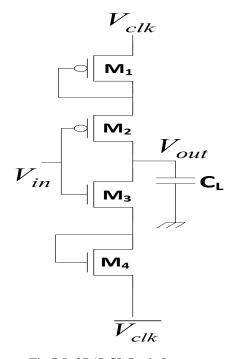

| Fig.3.9: Basic IDFAL circuit                                                       | 70       |

| Fig.3.10: Equivalent RC model of IDFAL                                             | 70       |

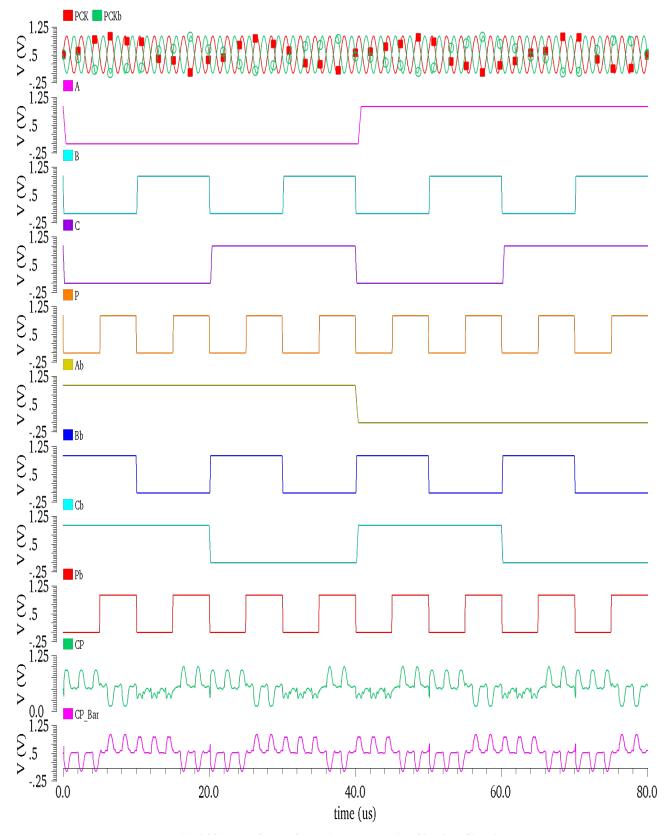

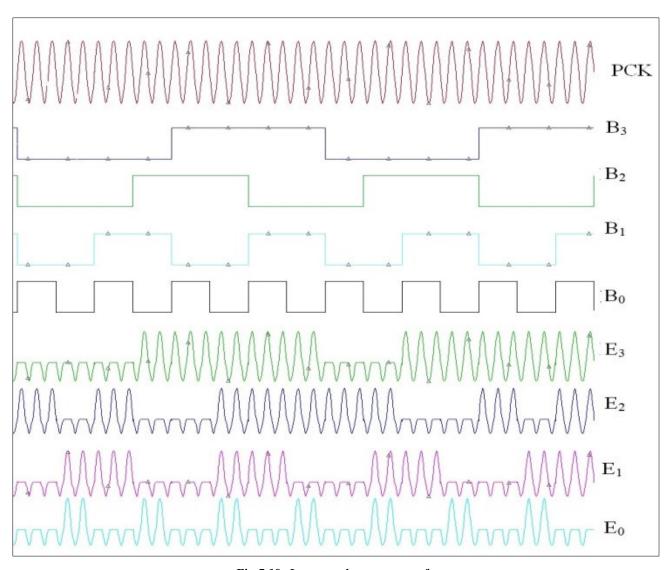

| Fig.3.11: A timing diagram of IDFAL                                                | 71       |

| Fig.3.12: Basic inverter circuit                                                   | 77       |

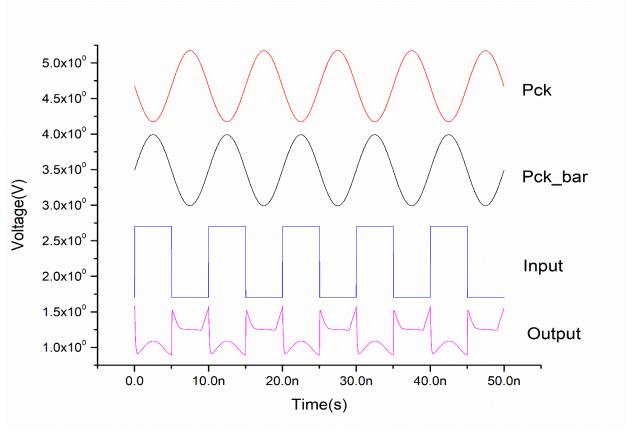

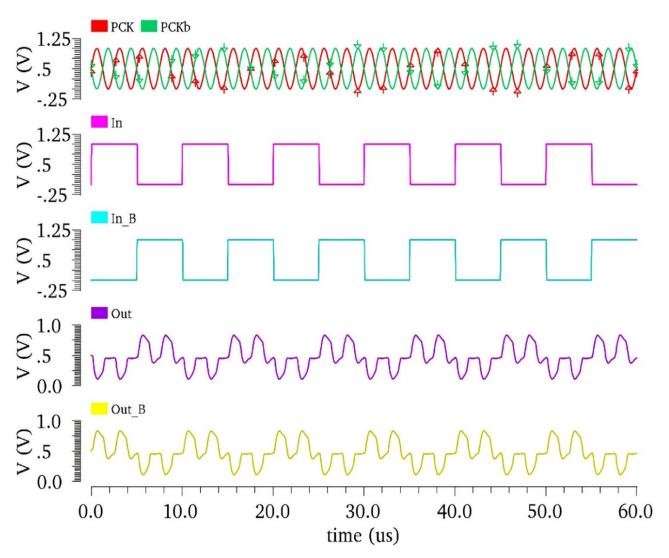

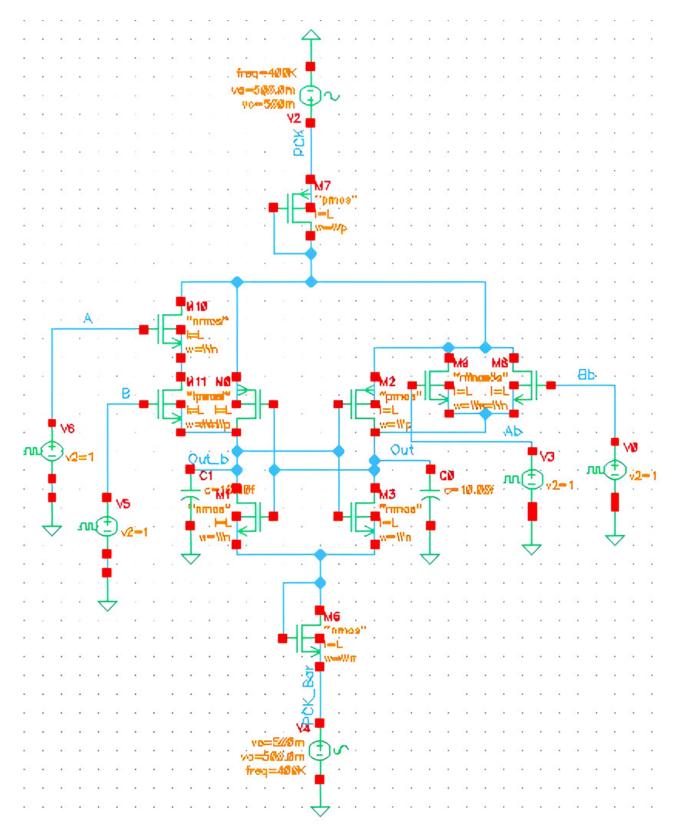

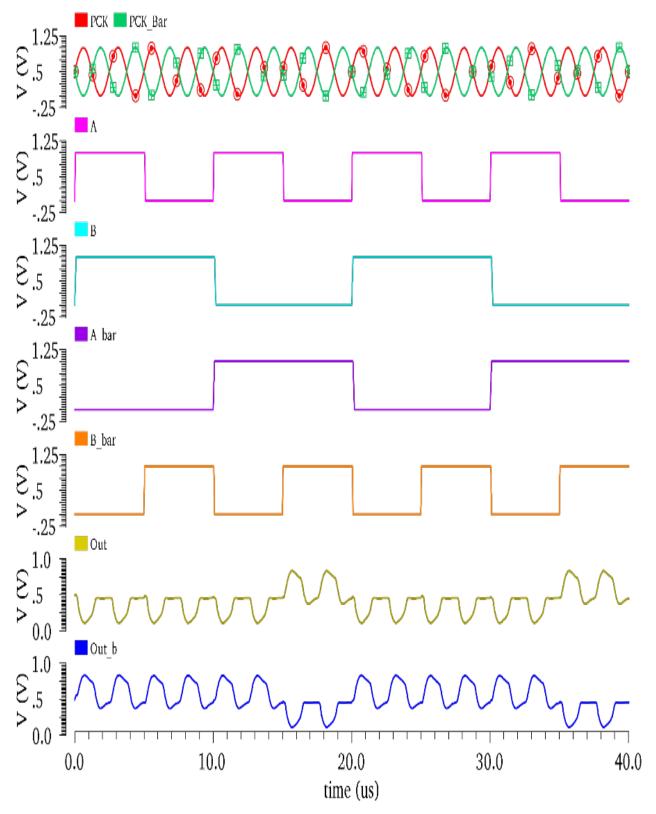

| Fig.3.13: Waveform of the IDFAL inverter circuit                                   | 78       |

| Fig.3.14: IDFAL NAND gate                                                          | 79       |

| Fig.3.15: Waveform of IDFAL NAND gate                                              | 80       |

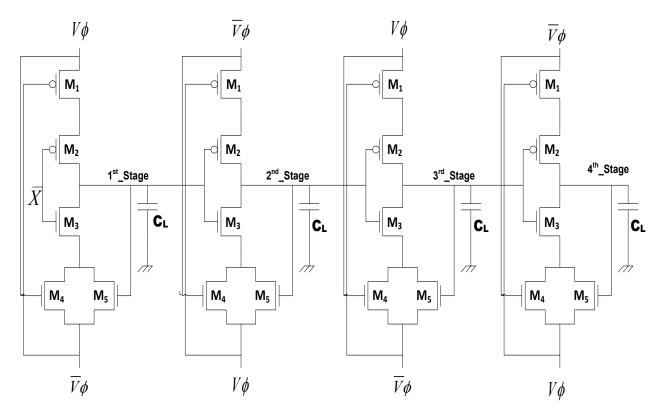

| Fig.3.16: Pipelining of IDFAL inverter                                             | 81       |

| Fig.3.17: Waveform of IDFAL inverter chain                                         | 81       |

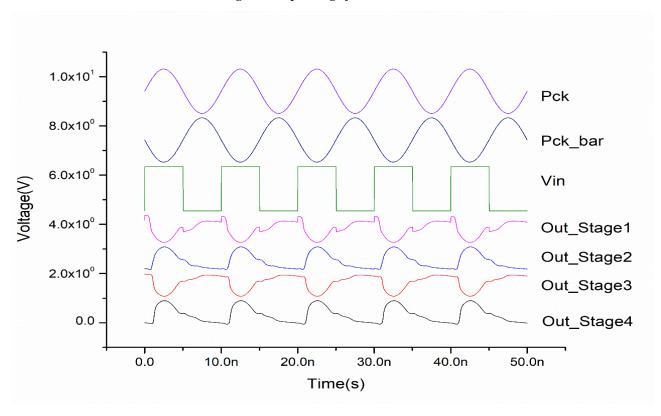

| Fig.3.18: IDFAL SR flip-flop                                                       | 82       |

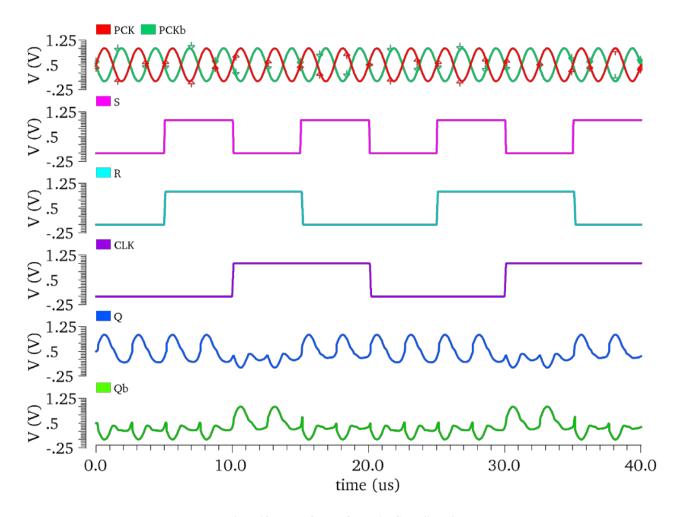

| Fig.3.19: Waveform of IDFAL SR flip-flop                                                                                                      | 83  |

|-----------------------------------------------------------------------------------------------------------------------------------------------|-----|

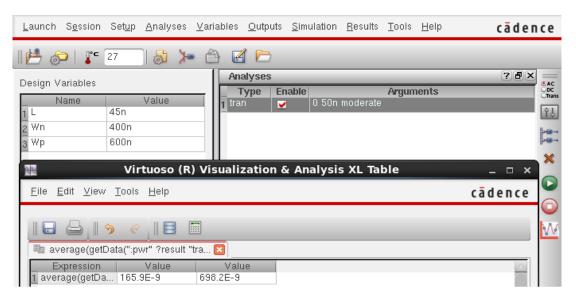

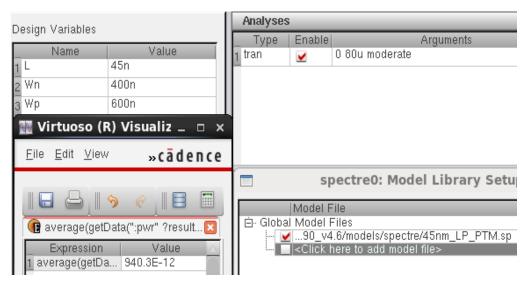

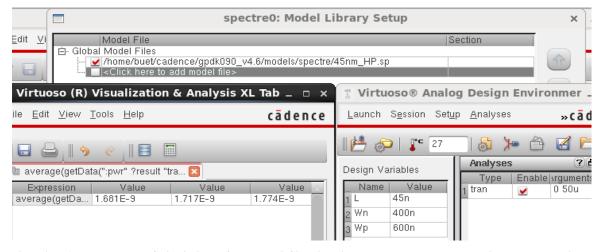

| <b>Fig.3.20:</b> Analog design environment showing simulation parameters and the result of average power consumption in the analysis XL table | 84  |

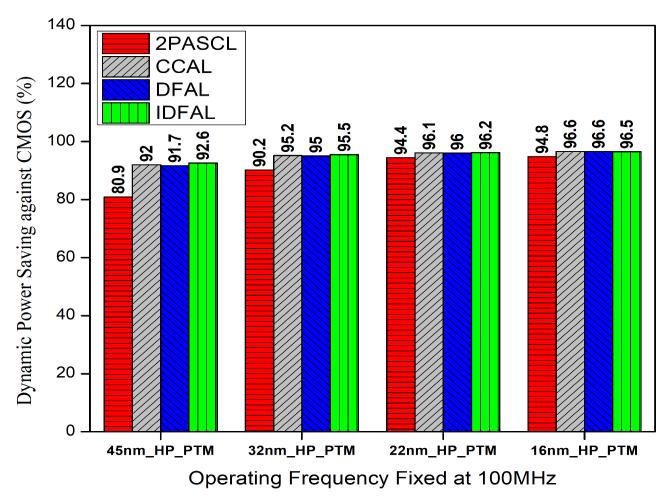

| <b>Fig.3.21:</b> Dynamic power saving of adiabatic inverter circuit against conventional CMOS                                                 | 92  |

| Fig.4.1: Basic IDFAL circuit                                                                                                                  | 96  |

| Fig.4.2: Basic inverter of 2PASLC                                                                                                             | 96  |

| Fig.4.3: Basic inverter of ADCL                                                                                                               | 97  |

| Fig.4.4: Basic inverter of DFAL                                                                                                               | 97  |

| Fig.4.5: Basic inverter of QSERL                                                                                                              | 97  |

| Fig.4.6: Basic inverter of 2PADCL                                                                                                             | 97  |

| Fig.4.7: Basic inverter of CCAL                                                                                                               | 98  |

| Fig.4.8: Basic inverter circuit                                                                                                               | 100 |

| Fig.4.9: Waveform of the IDFAL inverter circuit                                                                                               | 101 |

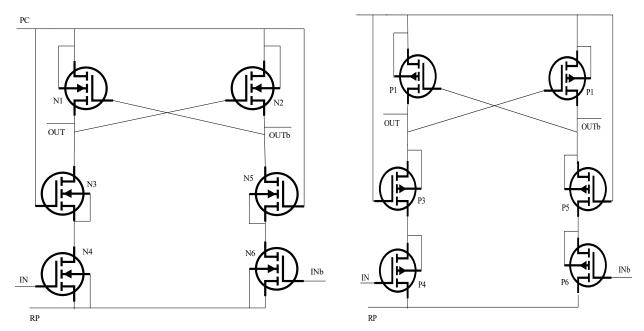

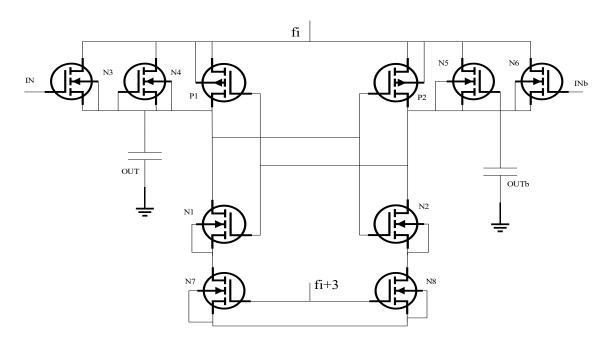

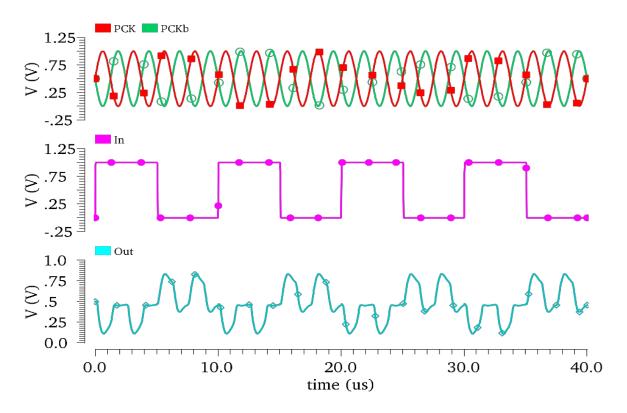

| Fig.4.10: SR flip-flop logic diagram                                                                                                          | 102 |

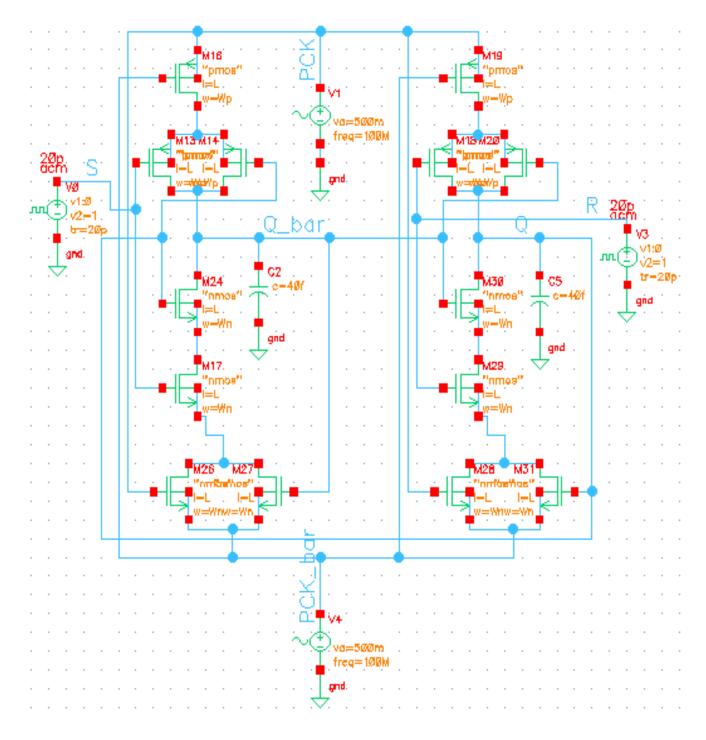

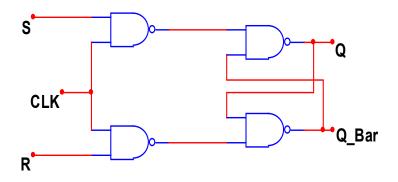

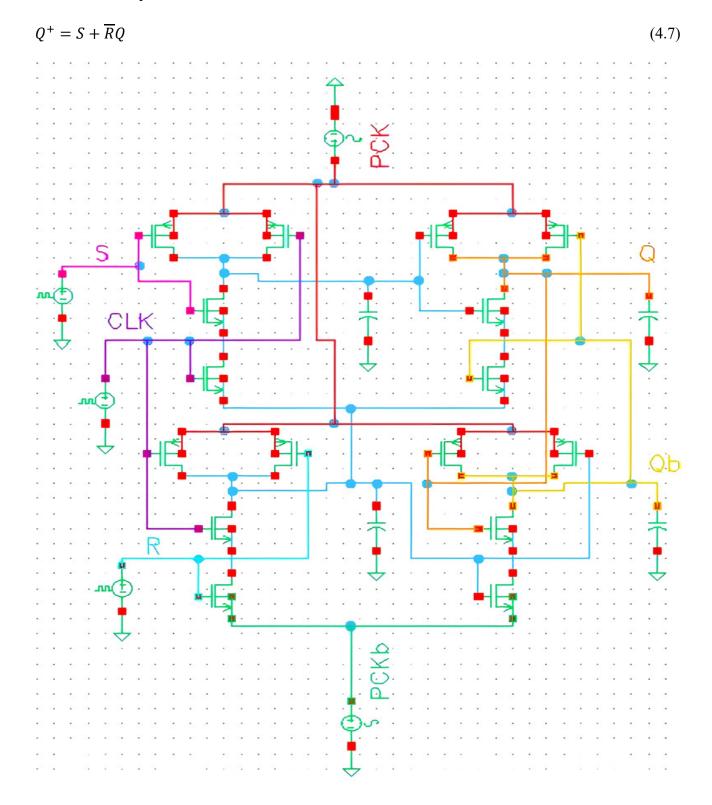

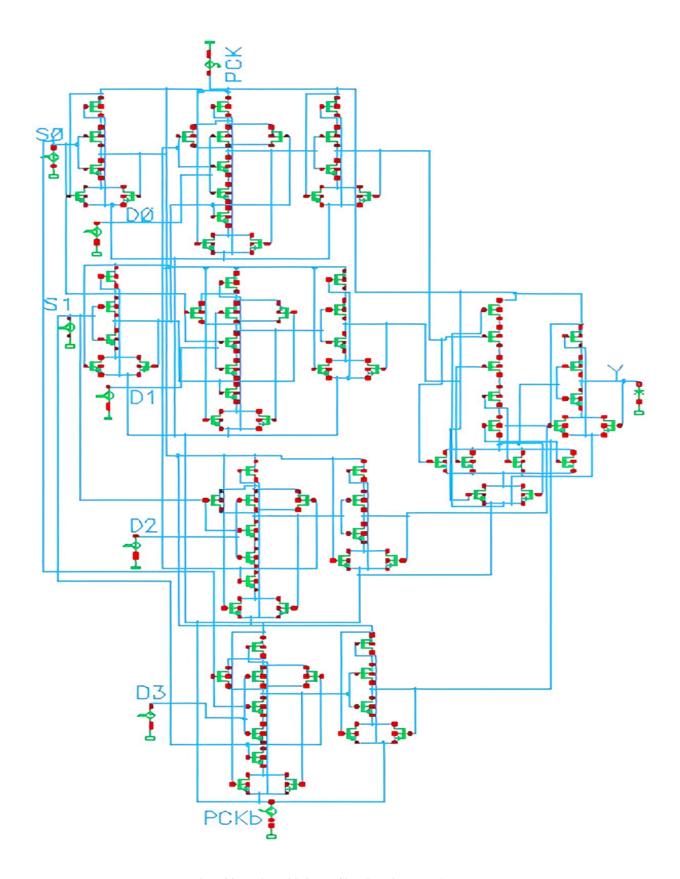

| Fig.4.11: IDFAL SR flip-flop                                                                                                                  | 103 |

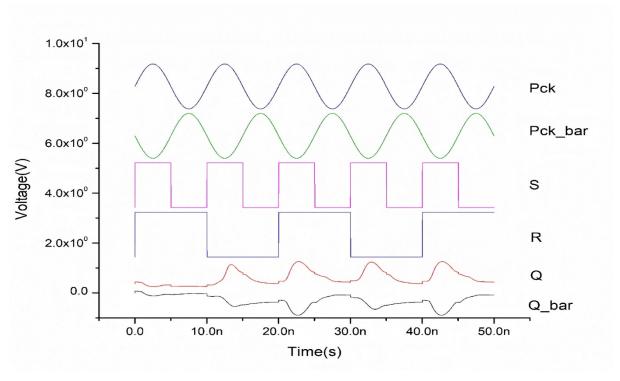

| Fig.4.12: Waveform if IDFAL SR flip-flop                                                                                                      | 104 |

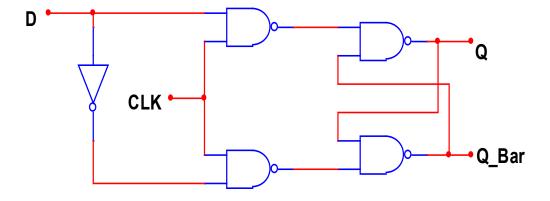

| Fig.4.13: D flip-flop logic diagram                                                                                                           | 105 |

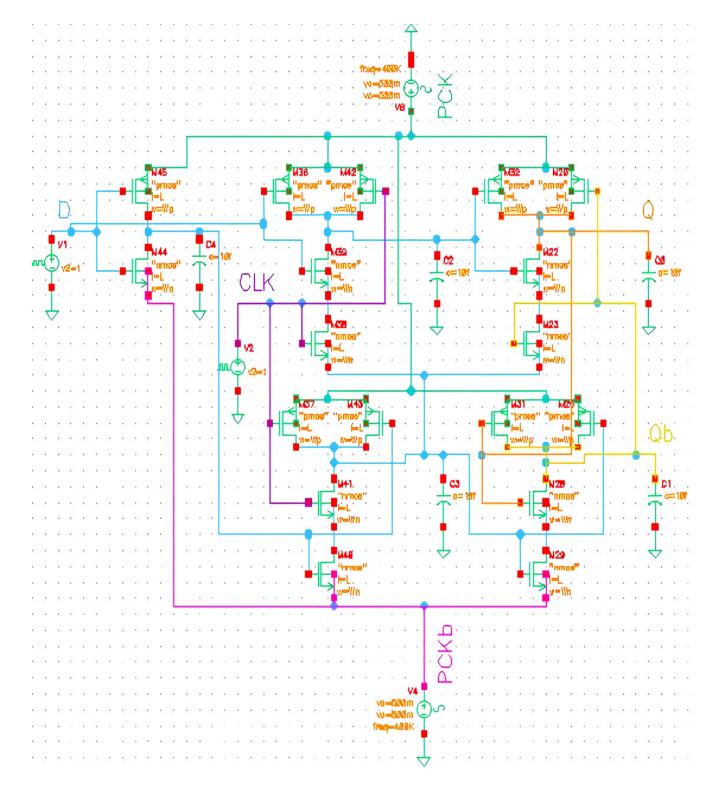

| Fig.4.14: IDFAL D flip-flop                                                                                                                   | 106 |

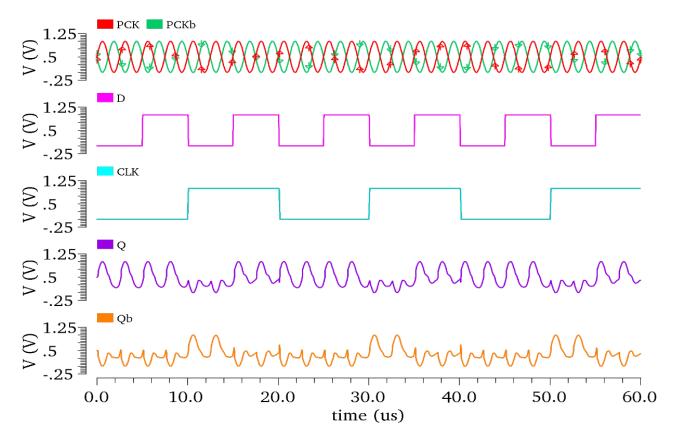

| Fig.4.15: Waveform of IDFAL D flip-flip                                                                                                       | 107 |

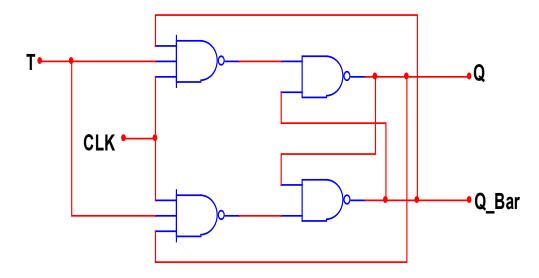

| Fig.4.16: T flip-flop logic diagram                                                                                                           | 108 |

| Fig.4.17: IDFAL T flip-flop                                                                                                                   | 109 |

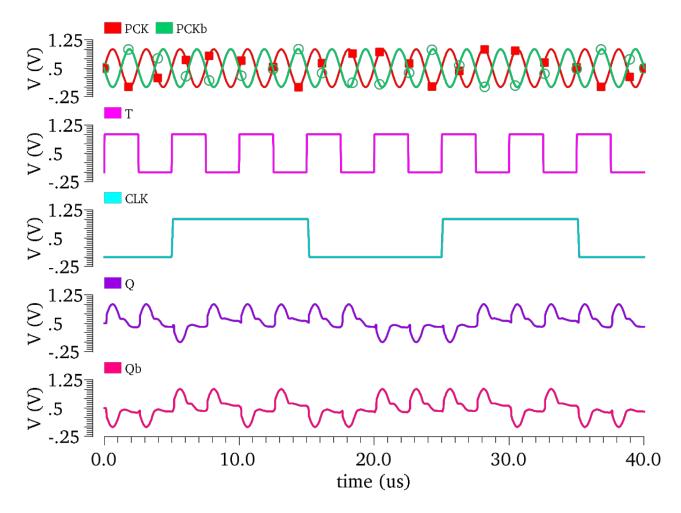

| Fig.4.18: Waveform of IDFAL T flip-flop                                                                                                       | 110 |

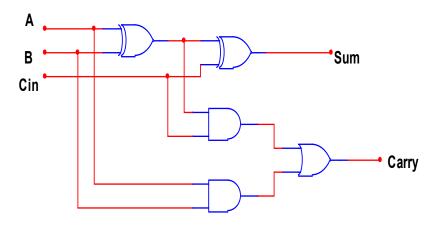

| Fig.4.19: Full adder logic diagram                                                                                                            | 111 |

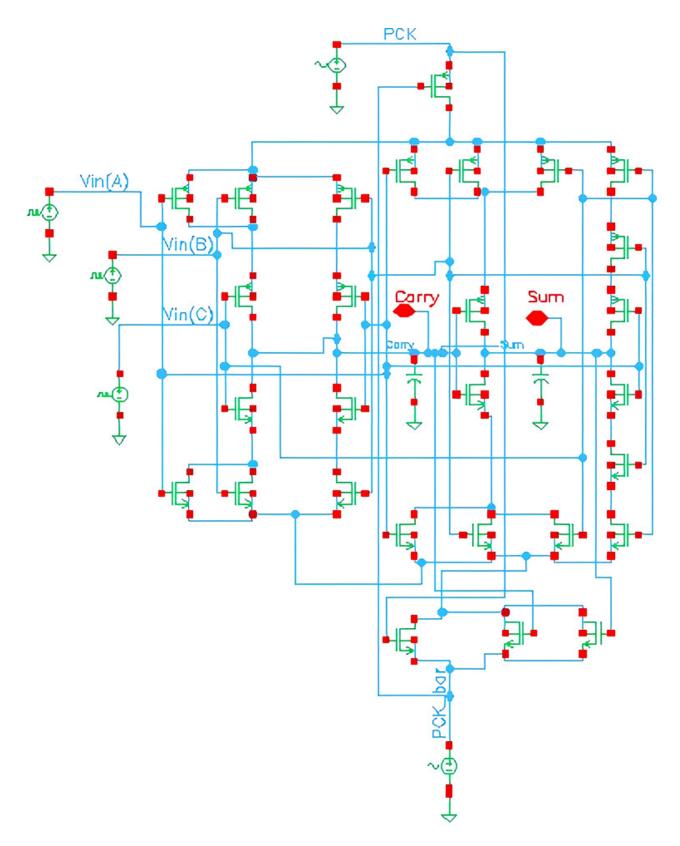

| Fig.4.20: Full adder circuit using IDFAL                                                                                                      | 112 |

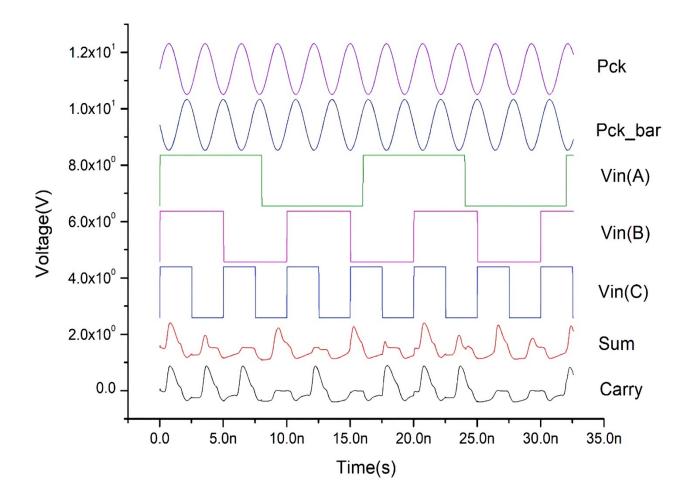

| Fig.4.21: Waveform of IDFAL full adder                                                                                                        | 113 |

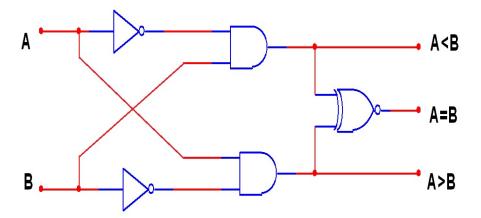

| Fig.4.22: Logic diagram of a I-Bit comparator                                                                                                 | 114 |

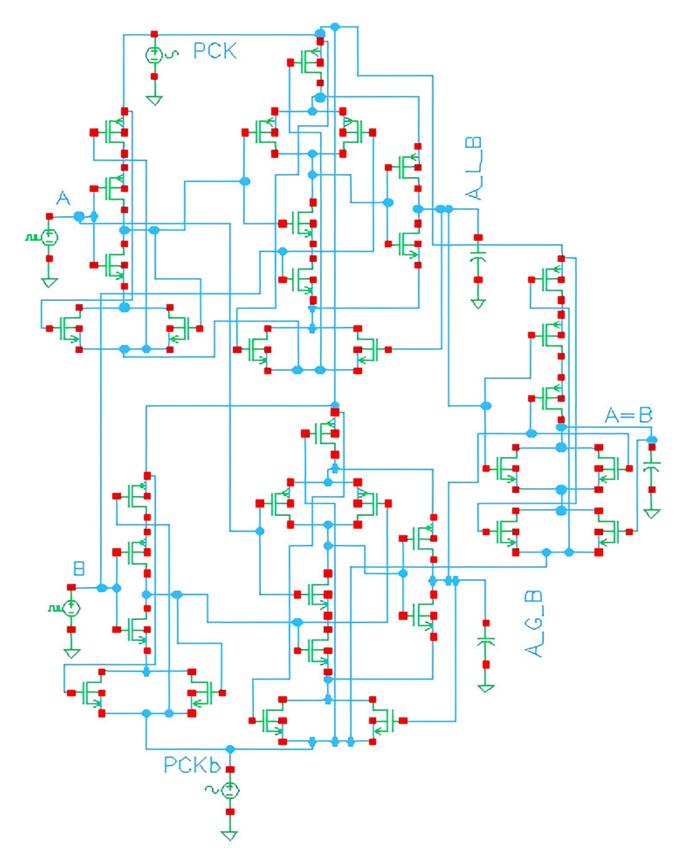

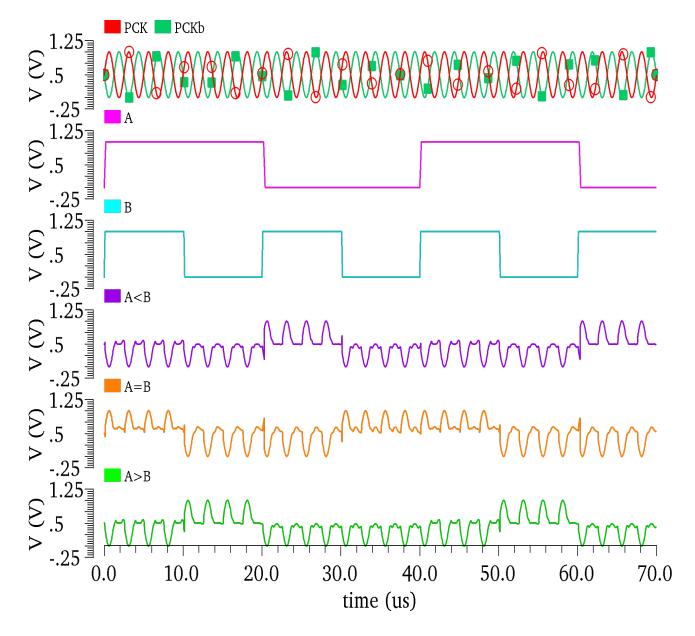

| Fig.4.23: I-Bit comparator circuit using IDFAL                                                                                                | 115 |

| Fig.4.24: Waveform of IDFAL I-Bit comparator                                                                                                  | 116 |

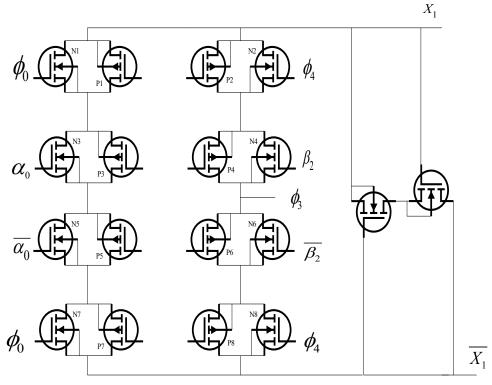

| Fig.4.25: Logic diagram of a 2x4 decoder                                                                                                      | 118 |

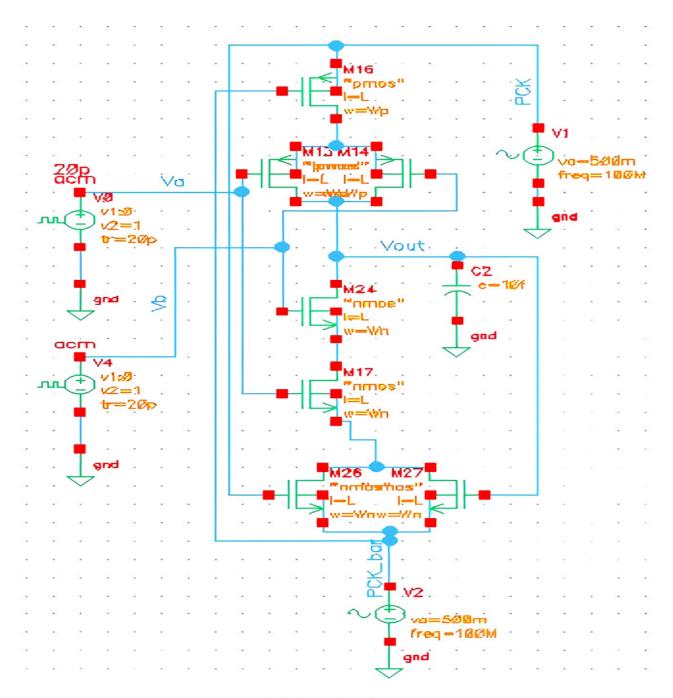

| Fig.4.26: 2x4 decoder circuit using IDFAL                                                                                                     | 119 |

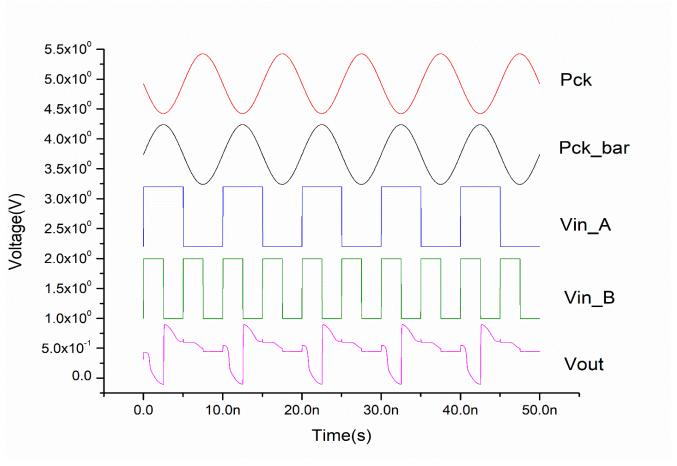

| Fig.4.27: Waveform of IDFAL 2x4 decoder circuit                                                                                               | 120 |

| Fig.4.28: Logic diagram of a 4x1 Multiplexer                                                                                                  | 122 |

| Fig.4.29: 4x1 multiplexer circuit using IDFAL                                                                                                 | 123 |

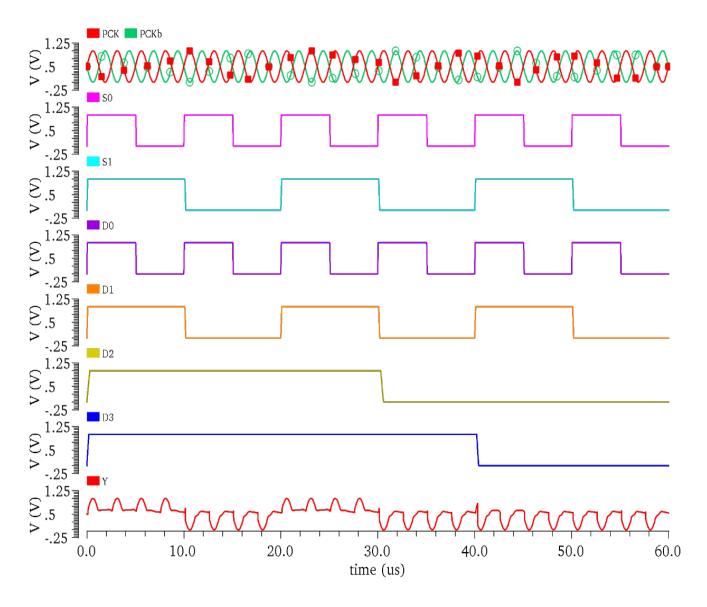

| Fig.4.30: Waveform of IDFAL 4x1 multiplexer circuit                                                                      | 124 |

|--------------------------------------------------------------------------------------------------------------------------|-----|

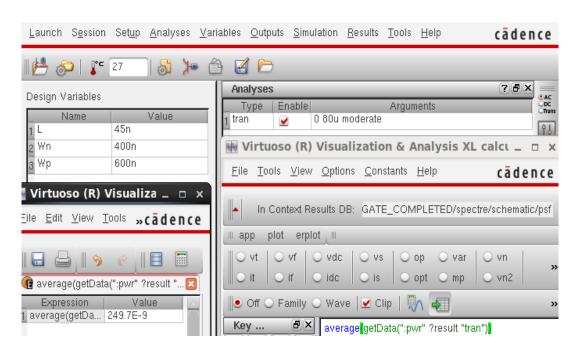

| Fig.4.31: Simulation settings and average power usage in the analysis XL                                                 | 125 |

| table in analog design environment                                                                                       |     |

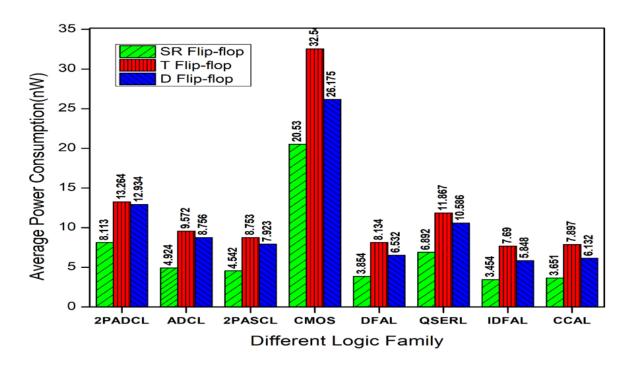

| Fig.4.32: Average power consumption of sequential circuits using                                                         | 126 |

| 45nm_LP_PTM, within 4 clock cycles at 100 KH                                                                             |     |

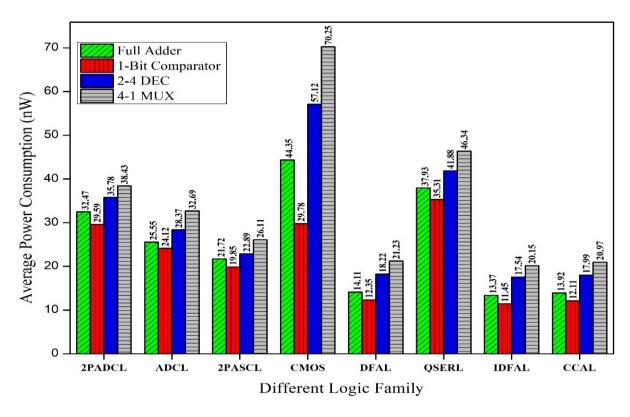

| <b>Fig.4.33:</b> Average power consumption of combinational circuits using 45nm_LP_PTM, within 4 clock cycles at 400 KHz | 126 |

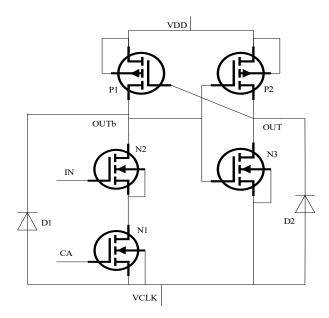

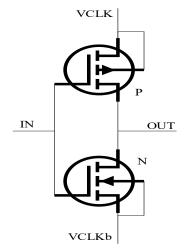

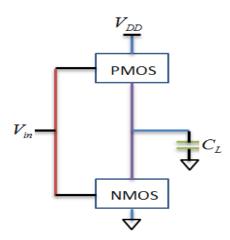

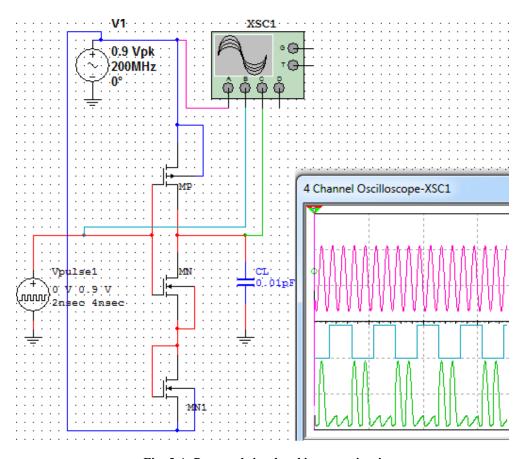

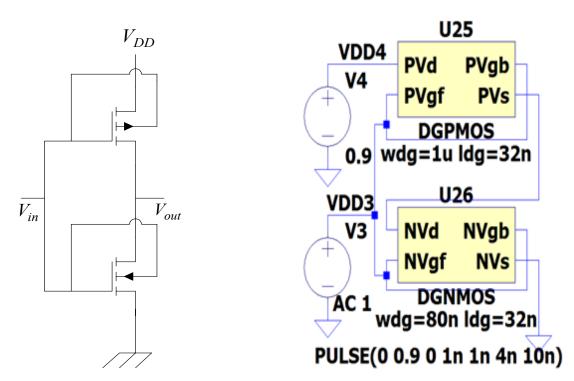

| Fig. 5.1: Schematic of CMOS Inverter                                                                                     | 130 |

| Fig. 5.2: Adiabatic switching technique                                                                                  | 131 |

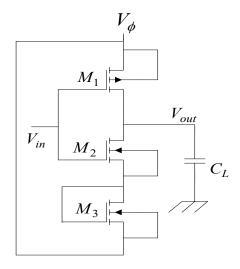

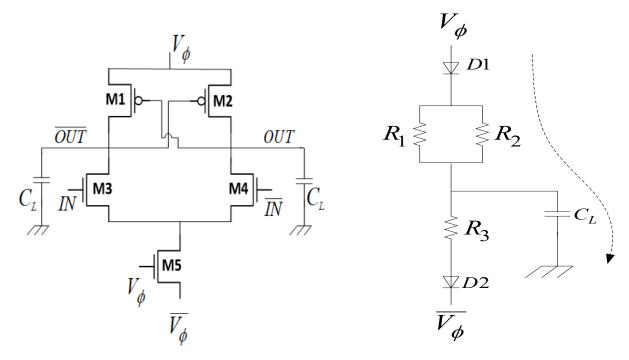

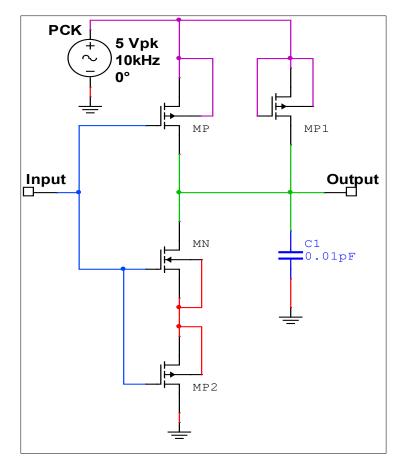

| Fig.5.3: Proposed inverter circuit                                                                                       | 133 |

| Fig.5.4: Proposed simulated inverter circuit                                                                             | 134 |

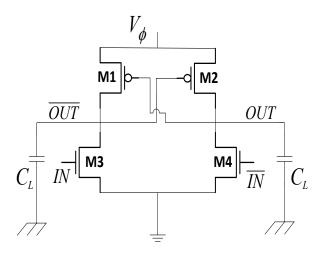

| Fig.5.5: Schematic of proposed FinFET Inverter circuit in SG mode                                                        | 135 |

| Fig.5.6: Simulated proposed FinFET Inverter circuit in SG mode                                                           | 135 |

| Fig.5.7: FinFET Inverter in LP mode                                                                                      | 136 |

| Fig.5.8: CMOS Inverter at 32nm Barkley PTM technology                                                                    | 136 |

| Fig.5.9: Power analysis of basic inverter using MOSFET                                                                   | 137 |

| Fig.5.10: Power analysis of basic inverter using FinFET                                                                  | 138 |

| Fig.5.11: Power analysis of adiabatic basic inverter using FinFET                                                        | 138 |

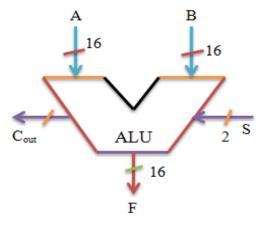

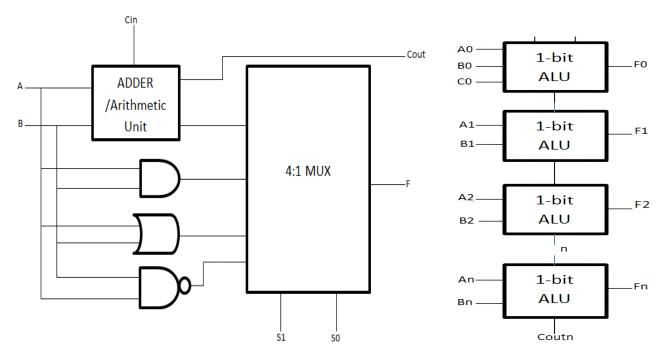

| Fig.5.12: 16-bit ALU                                                                                                     | 139 |

| Fig.5.13: Block diagram of basic 1-bit ALU                                                                               | 140 |

| Fig.5.14: Block diagram of n-bit ALU by cascading 1-bit ALU                                                              | 140 |

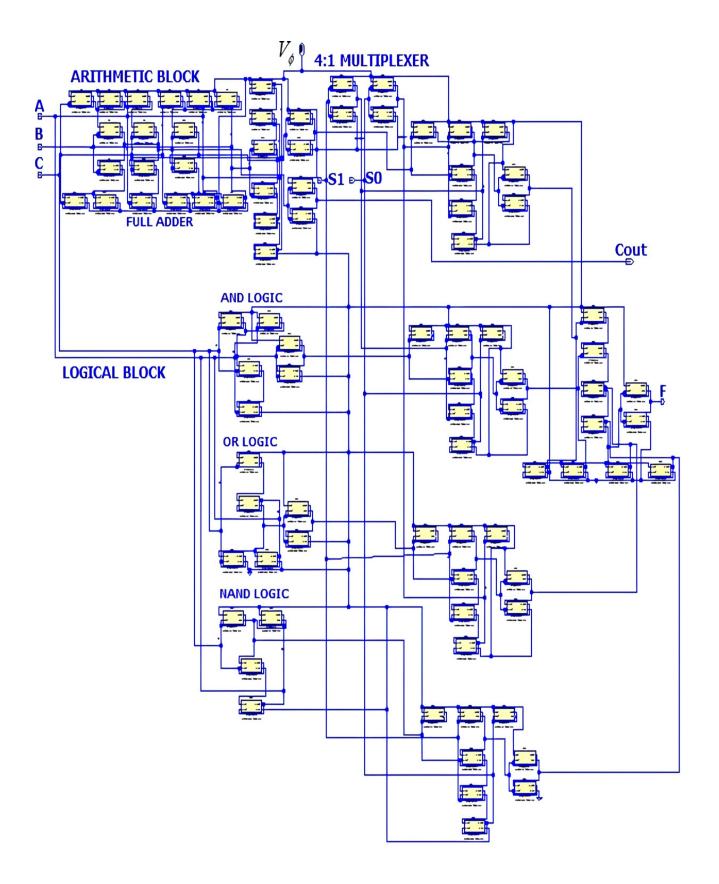

| Fig.5.15: Proposed 1-bit ALU using FinFET                                                                                | 141 |

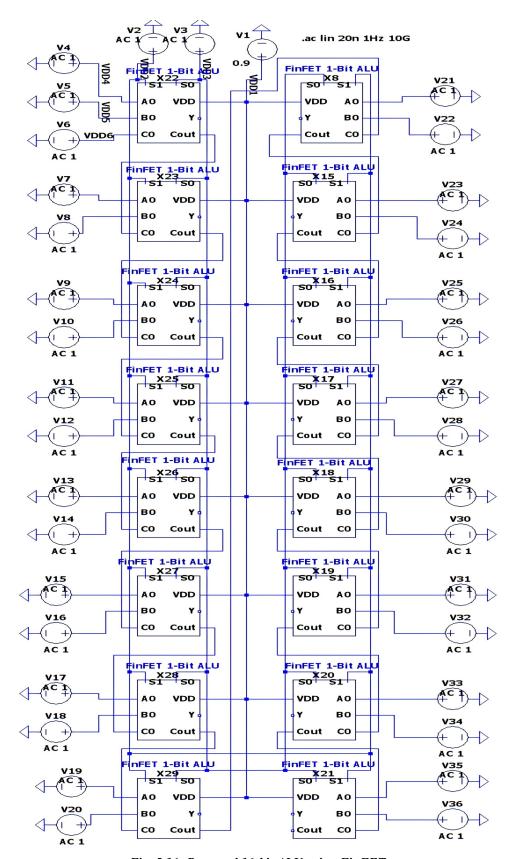

| Fig.5.16: Proposed 16-bit ALU using FinFET                                                                               | 142 |

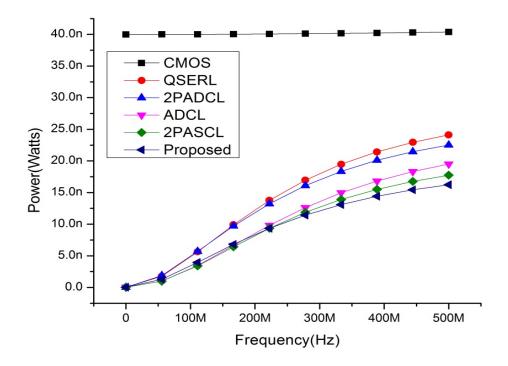

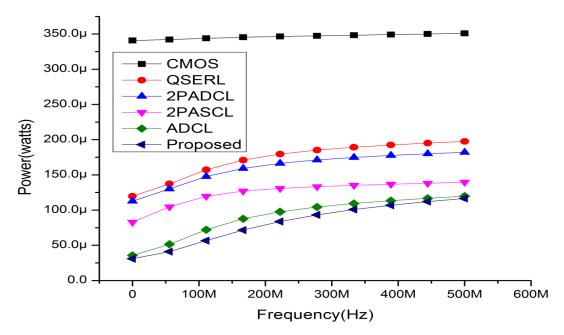

| Fig.5.17: Power evaluation of 16-bit ALU using MOSFET                                                                    | 143 |

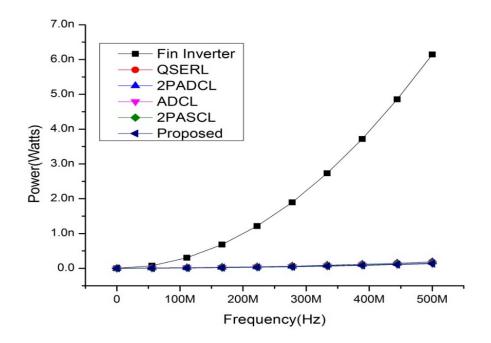

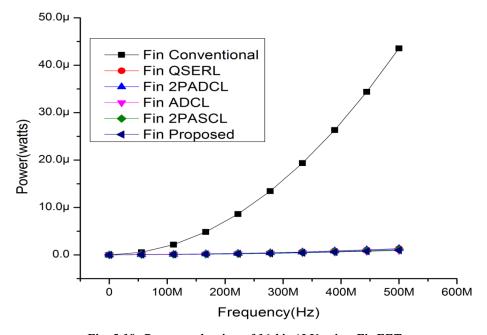

| Fig.5.18: Power evaluation of adiabatic 16-bit ALU using FinFET                                                          | 144 |

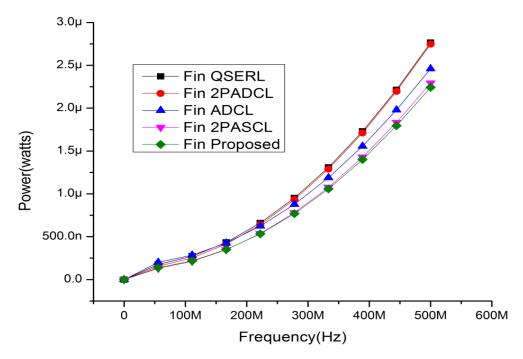

| Fig.5.19: Power evaluation of 16-bit ALU using FinFET                                                                    | 144 |

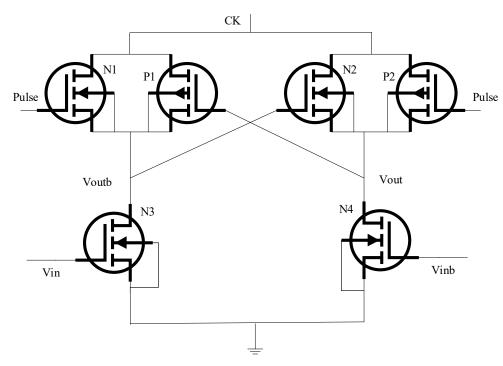

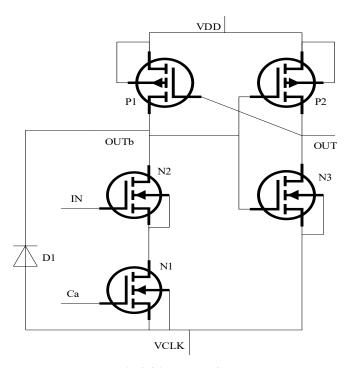

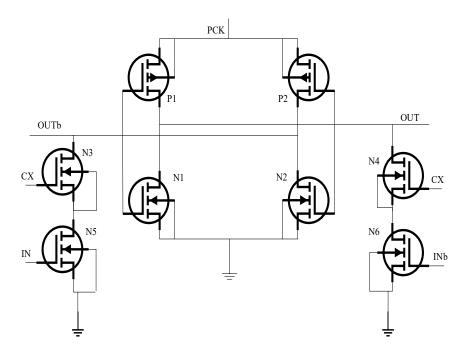

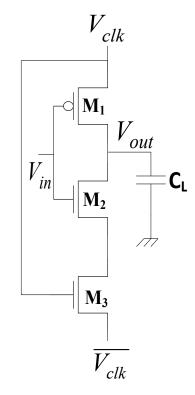

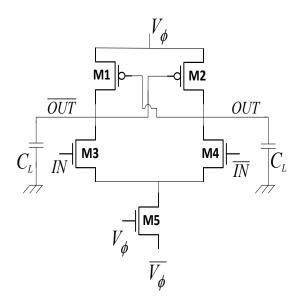

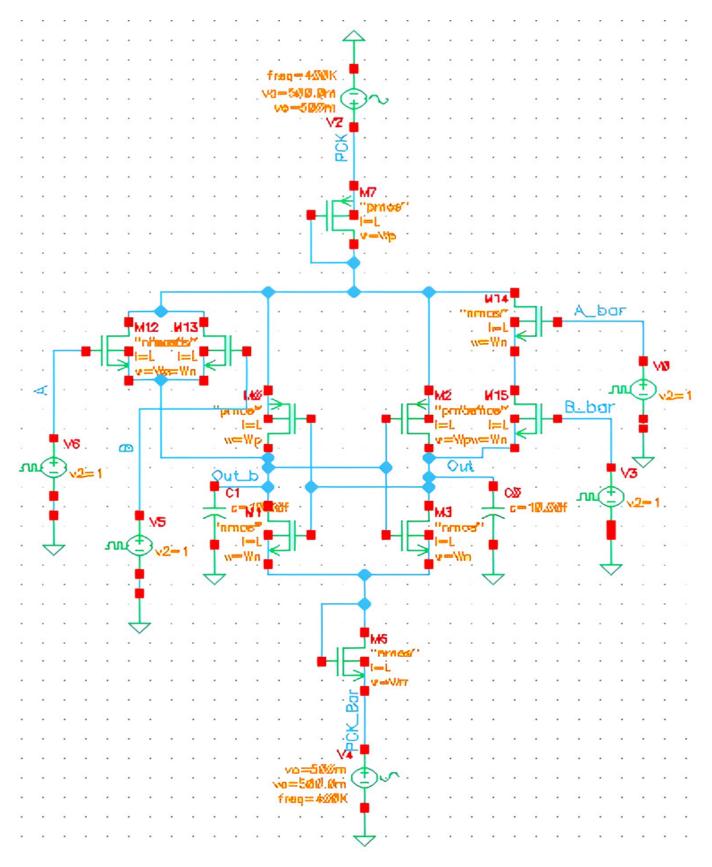

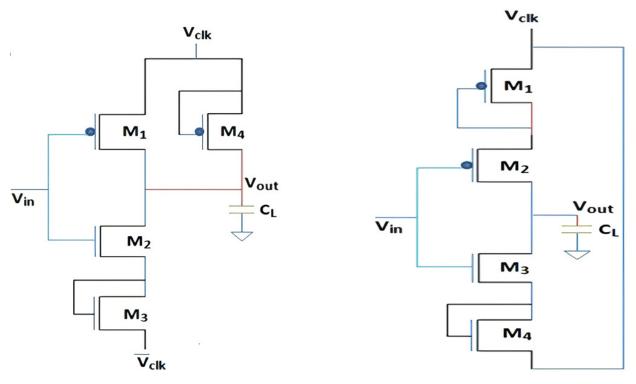

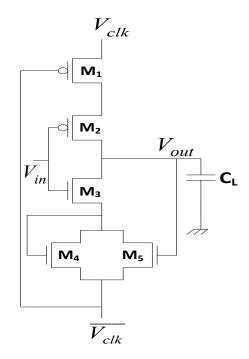

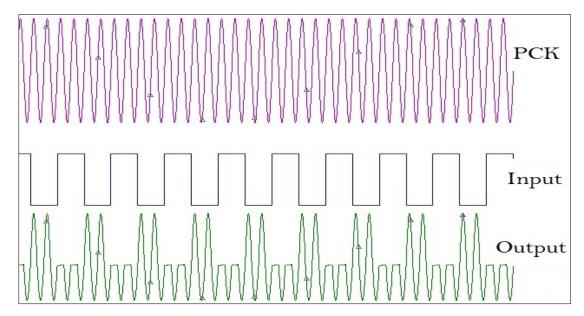

| Fig.6.1: Structure of EPFAL                                                                                              | 149 |

| Fig. 6.2: RC-diode equivalent circuit of the right side the dual-rail of EPFAL                                           | 149 |

| Fig.6.3: ECRL inverter                                                                                                   | 153 |

| Fig.6.4: PFAL inverter                                                                                                   | 153 |

| <b>Fig.6.5:</b> 2N-2N2P inverter                                                                                         | 153 |

| Fig.6.6: IPGAL inverter                                                                                                  | 153 |

| Fig. 6.7: 2P-PFAL inverter                                                                                               | 154 |

| Fig.6.8: CD-CAL inverter                                                                                                 | 154 |

| Fig.6.9: CD-PAL inverter                                                                                                                                                    | 154 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Fig.6.10: A-DCVSL inverter                                                                                                                                                  | 154 |

| <b>Fig.6.11:</b> Simulation model and EPFAL Inverter average power Consumption at 100KHz in analogue design environment                                                     | 155 |

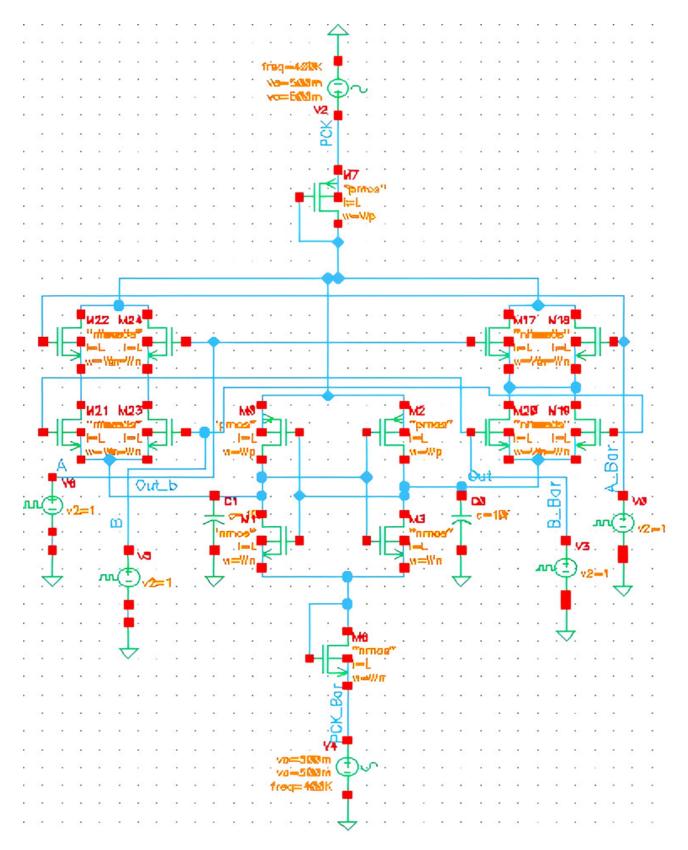

| Fig.6.12: EPFAL Inverter/Buffer Circuit                                                                                                                                     | 156 |

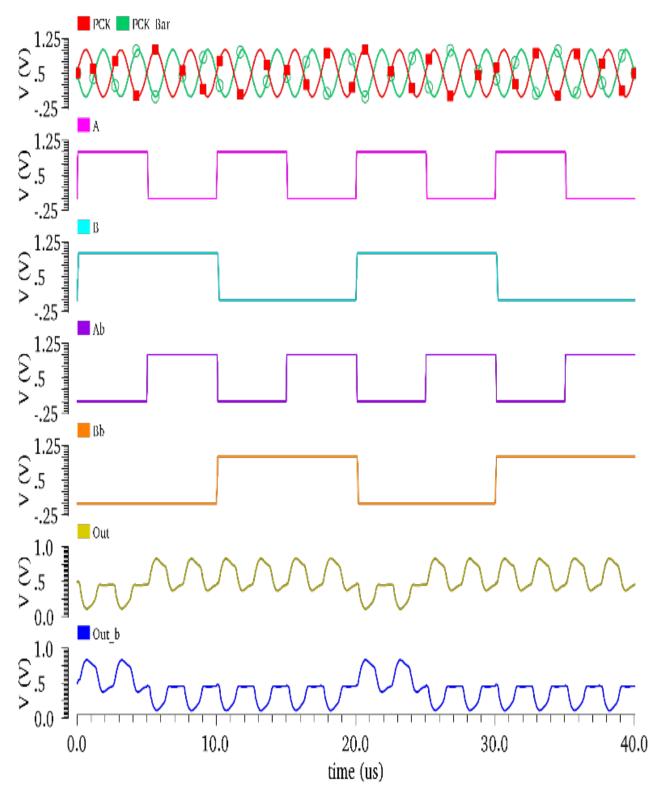

| Fig.6.13: Waveform of the EPFAL Inverter/Buffer Circuit                                                                                                                     | 157 |

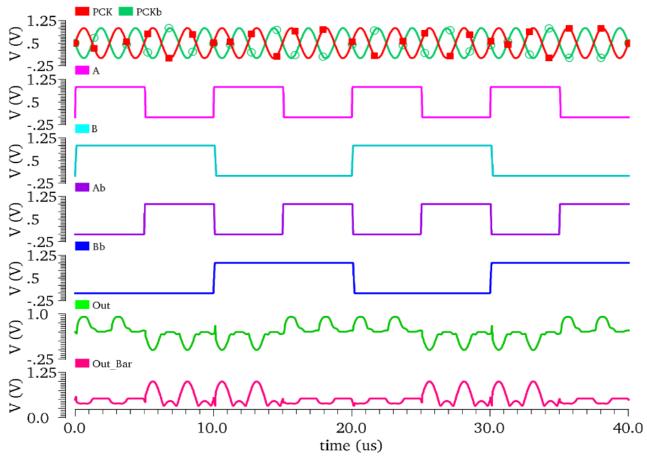

| Fig.6.14: EPFAL AND/NAND Circuit                                                                                                                                            | 158 |

| Fig.6.15: Waveform of the EPFAL NAND/AND Circuit                                                                                                                            | 159 |

| Fig.6.16: EPFAL NOR/ OR Circuit                                                                                                                                             | 160 |

| Fig.6.17: Waveform of the EPFAL NOR/OR Circuit                                                                                                                              | 161 |

| Fig.6.18: Waveform of the EPFAL XNOR/XOR Circuit                                                                                                                            | 162 |

| Fig.6.19: EPFAL XNOR/XOR Circuit                                                                                                                                            | 163 |

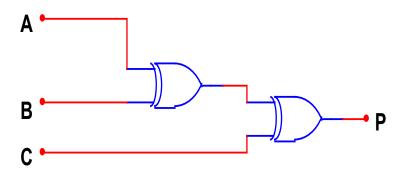

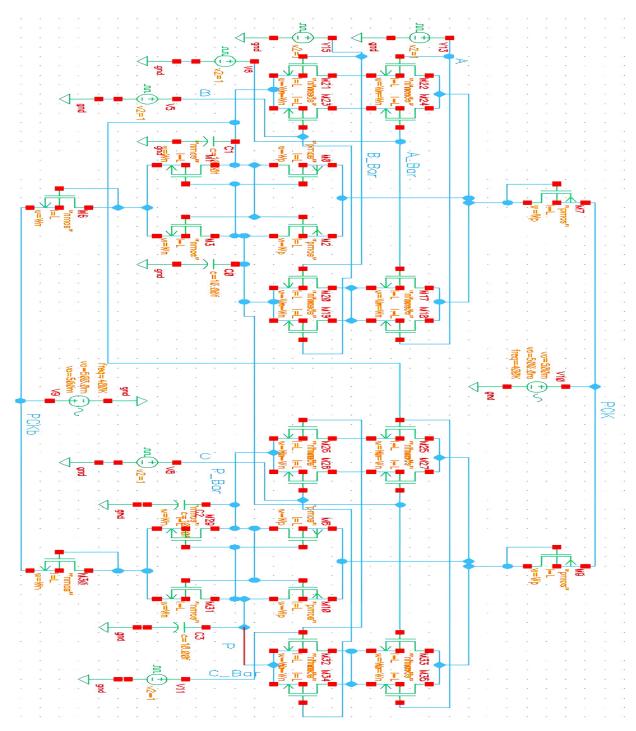

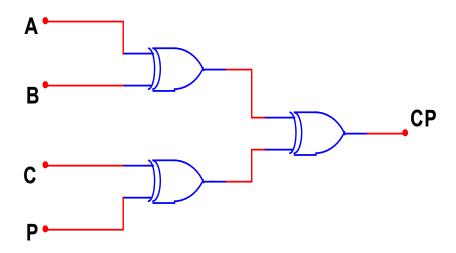

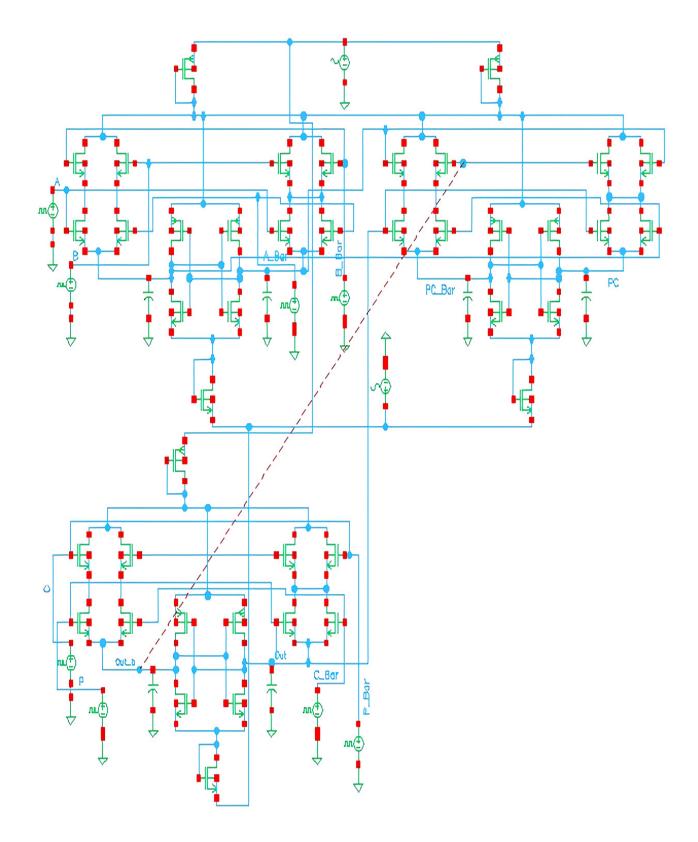

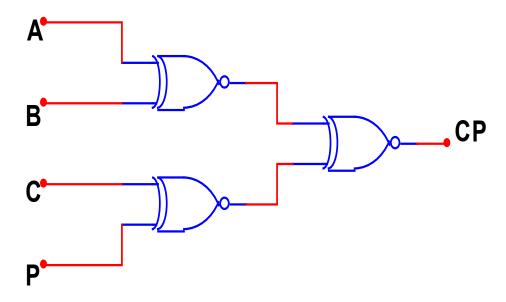

| Fig.6.20: Logic diagram of Even Parity Generator                                                                                                                            | 165 |

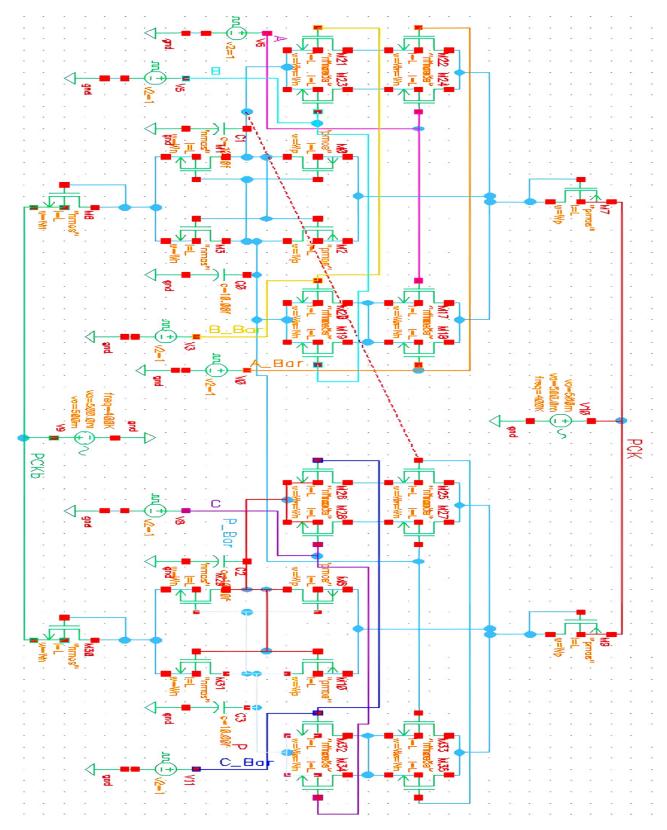

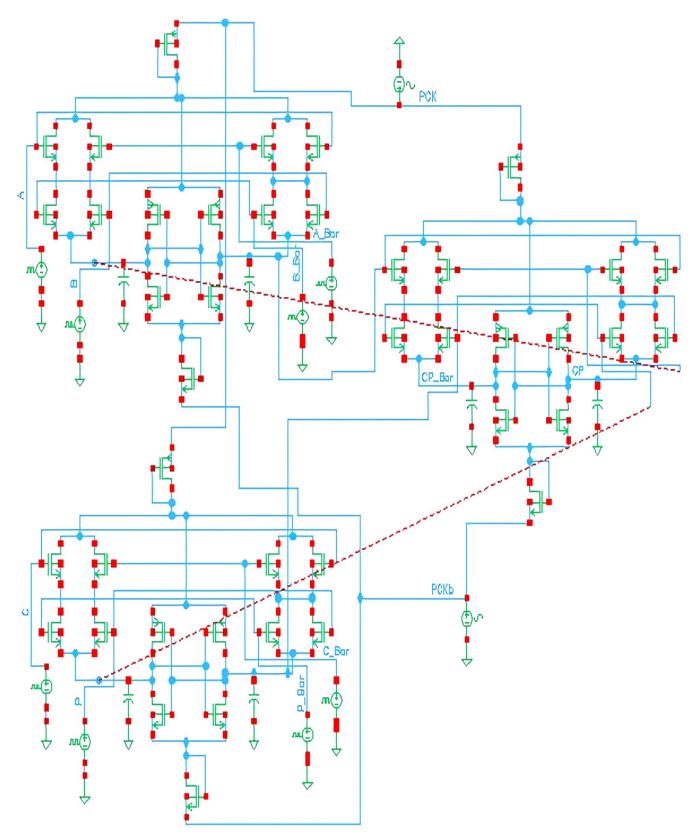

| Fig.6.21: EPFAL Even Parity Generator Circuit                                                                                                                               | 166 |

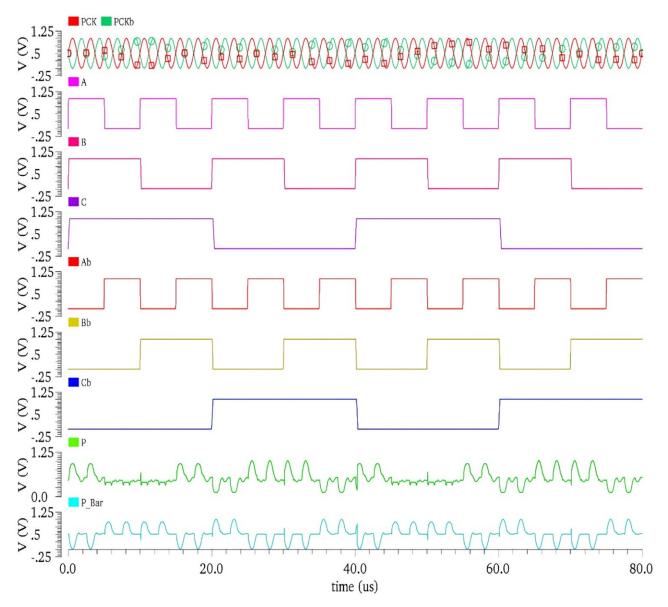

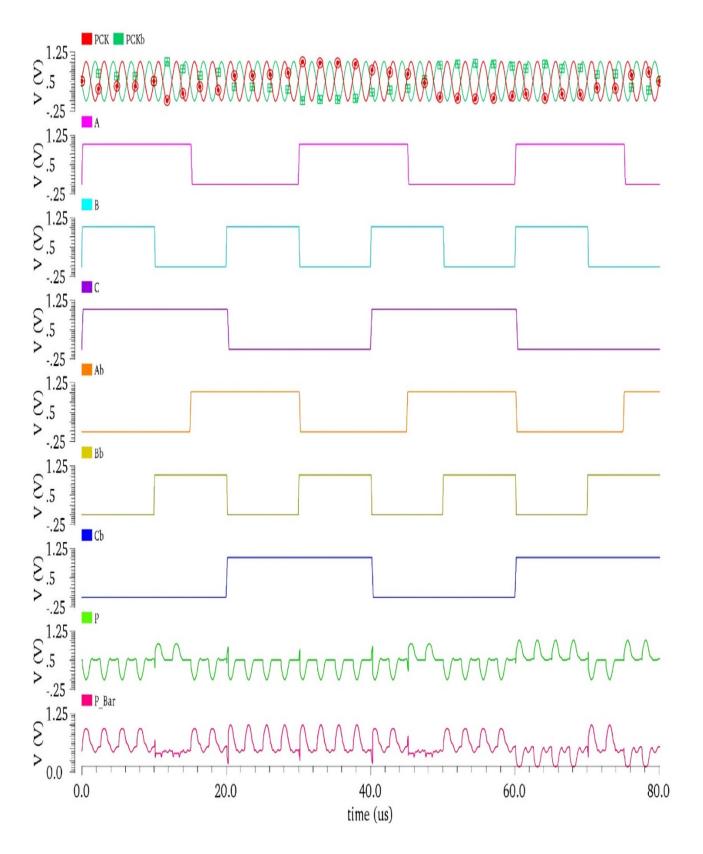

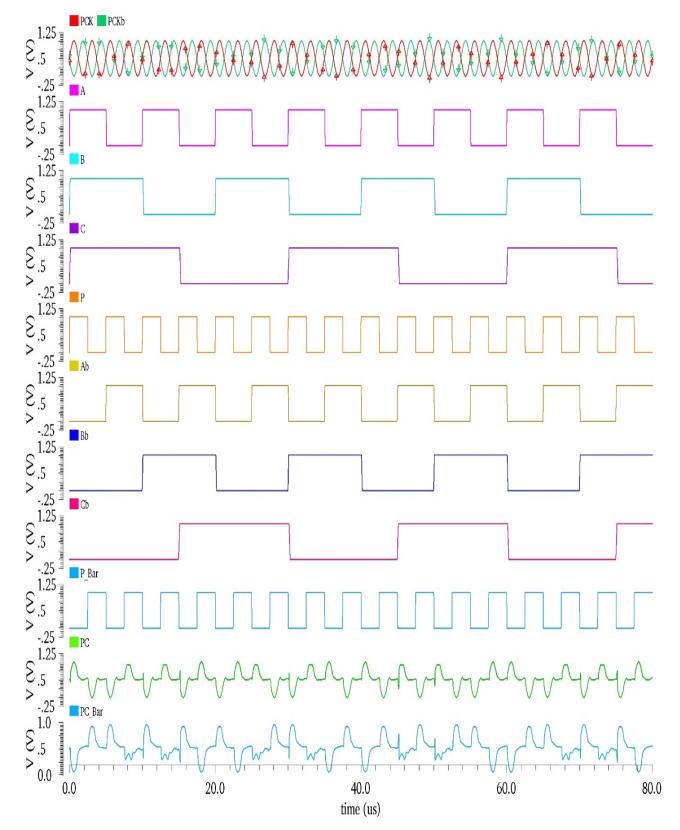

| Fig.6.22: Waveform of an EPFAL Even Parity Generator Circuit                                                                                                                | 167 |

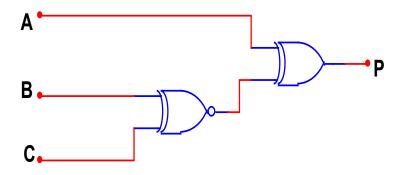

| Fig 6.23: Logic diagram of Odd Parity Generator                                                                                                                             | 168 |

| Fig.6.24: EPFAL Odd Parity Generator Circuit                                                                                                                                | 169 |

| Fig.6.25: Waveform of an EPFAL Odd Parity Generator Circuit                                                                                                                 | 170 |

| Fig.6.26: Logic diagram of Even Parity Checker                                                                                                                              | 172 |

| Fig.6.27: EPFAL Even Parity Checker Circuit                                                                                                                                 | 173 |

| Fig.6.28: Waveform of EPFAL Even Parity Checker Circuit                                                                                                                     | 174 |

| Fig.6.29: Logic diagram of Odd Parity Checker                                                                                                                               | 176 |

| Fig.6.30: EPFAL Odd Parity Checker Circuit                                                                                                                                  | 177 |

| Fig.6.31: Waveform of an EPFAL Odd Parity Checker Circuit                                                                                                                   | 178 |

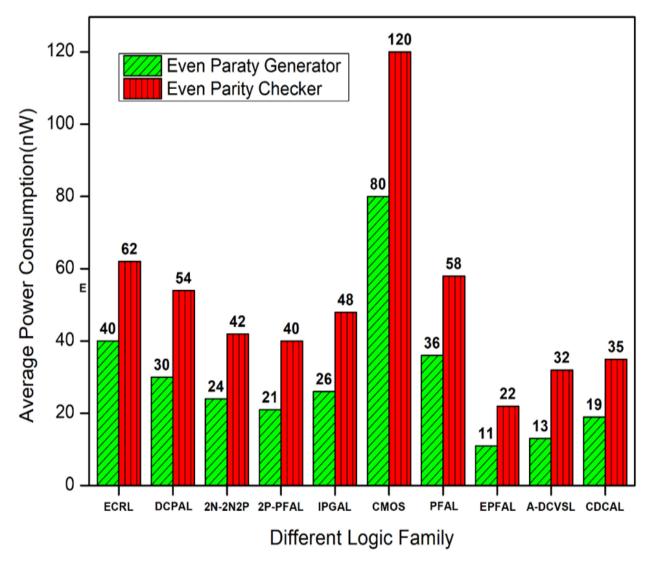

| <b>Fig.6.32:</b> Average dynamic power consumption of Even Parity Generator and Checker Circuits designed using traditional CMOS approach and several adiabatic literatures | 181 |

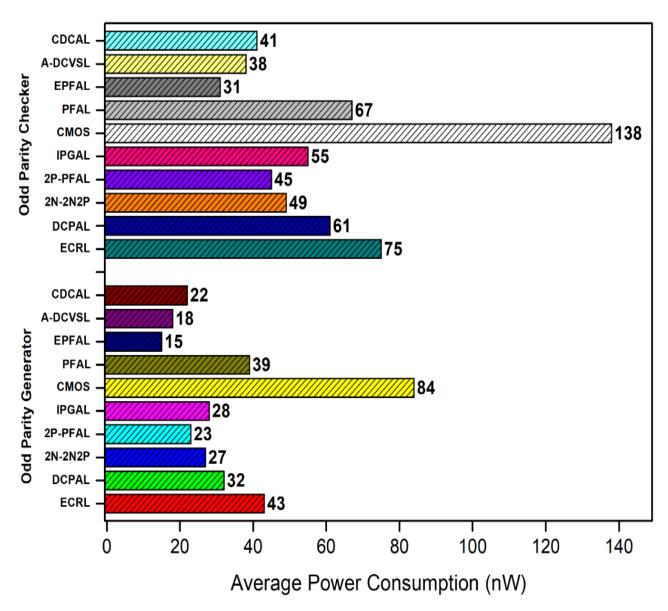

| <b>Fig.6.33:</b> Average dynamic power consumption of Odd Parity Generator and Checker Circuits designed using traditional CMOS approach and several adiabatic families     | 182 |

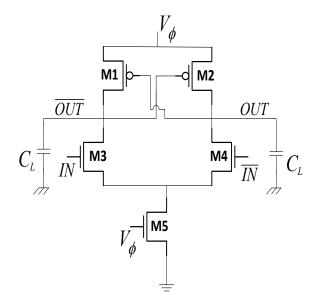

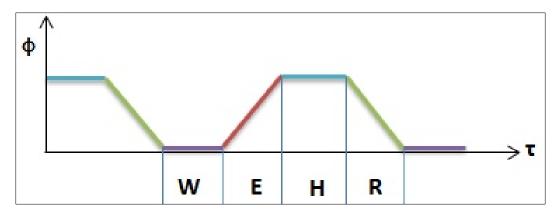

| Fig.7.1: Phases of power supply in adiabatic technique                                                                                                                      | 186 |

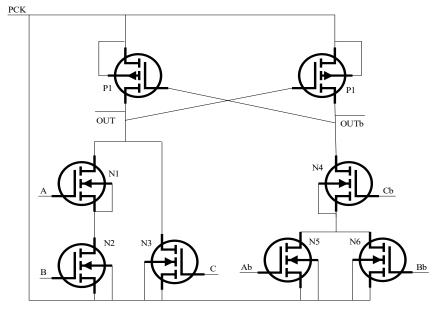

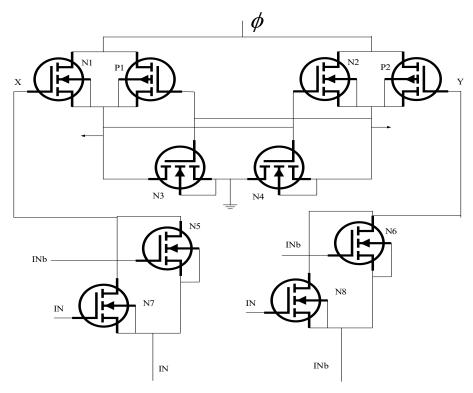

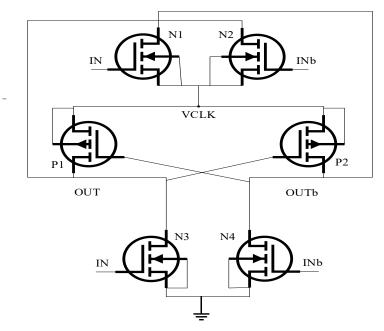

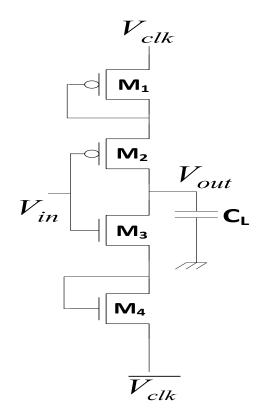

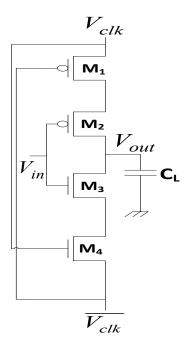

| Fig.7.2: 2PASCL Basic Inverter                                                                                                                                              | 186 |

| Fig.7.3: ADCL Basic Inverter                                                                                                                                                | 186 |

| Fig.7.4: QSERL Basic Inverter                                                                                                                                               | 187 |

| Fig.7.5: 2PADCL Basic Inverter                                                                                                                                              | 187 |

| Fig.7.6: CCAL Basic Inverter                                                                                                             | 187 |

|------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Fig.7.7: 2PADL Basic Inverter                                                                                                            | 187 |

| Fig.7.8: DFAL Basic Inverter                                                                                                             | 188 |

| Fig.7.9: A-DSCVL Basic Inverter                                                                                                          | 188 |

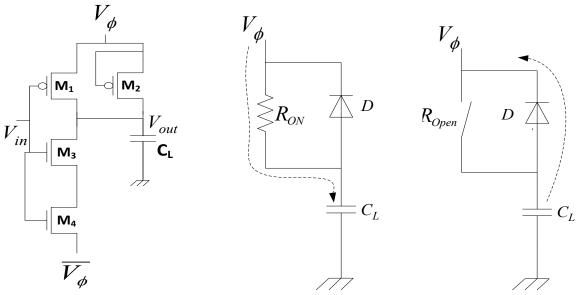

| Fig.7.10: Basic Inverter circuit of proposed logic                                                                                       | 189 |

| Fig.7.11: Basic Proposed Inverter Waveform                                                                                               | 190 |

| Fig.7.12: Schematic of the Proposed Basic Inverter                                                                                       | 191 |

| Fig.7.13: RC equivalent of The Proposed Inverter                                                                                         | 191 |

| Fig.7.14: RC equivalent of The Circuit when Discharging                                                                                  | 191 |

| <b>Fig.7.15:</b> Average Power Calculation of Proposed Circuit using 45nm-HP PTM at Various Frequencies                                  | 192 |

| <b>Fig.7.16:</b> Average Power Calculation of CMOS Circuit using 45nm-HP PTM at Various Frequencies                                      | 193 |

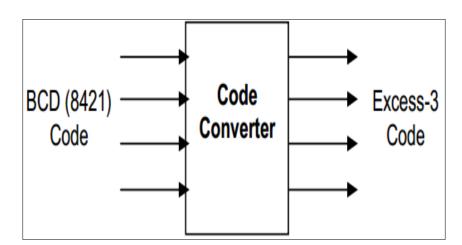

| Fig.7.17: Block diagram of BCD to excess-3 code converter                                                                                | 195 |

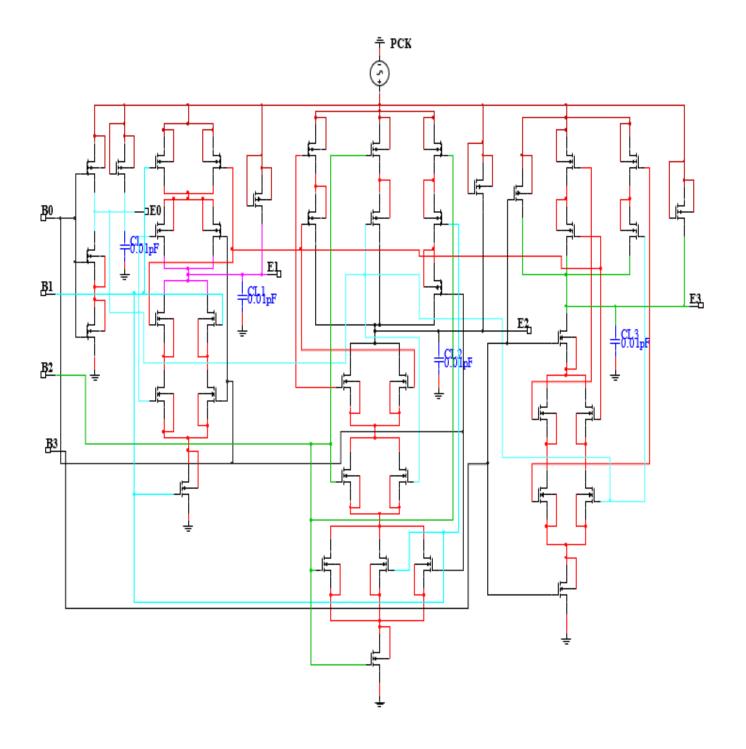

| Fig.7.18: Proposed circuit for BCD to Excess-3 code converter circuit                                                                    | 197 |

| Fig.7.19: Inputs and outputs waveforms for BCD code to Excess-3 code converter                                                           | 198 |

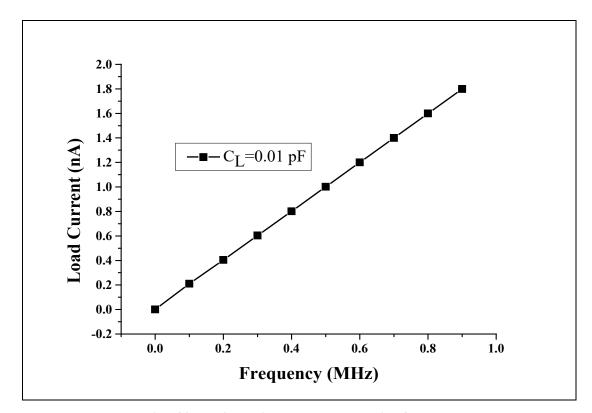

| Fig.7.20: Load capacitor current vs. operating frequency                                                                                 | 200 |

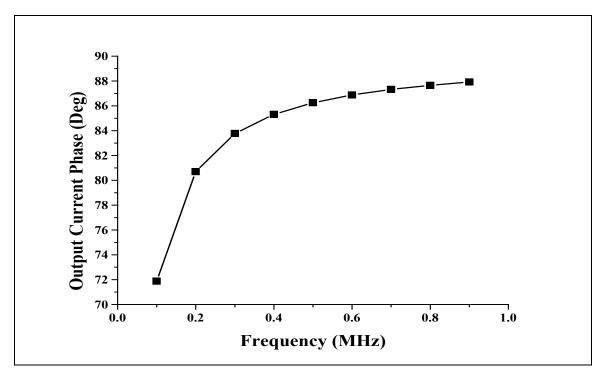

| Fig.7.21: Output current phase vs. operating frequency                                                                                   | 200 |

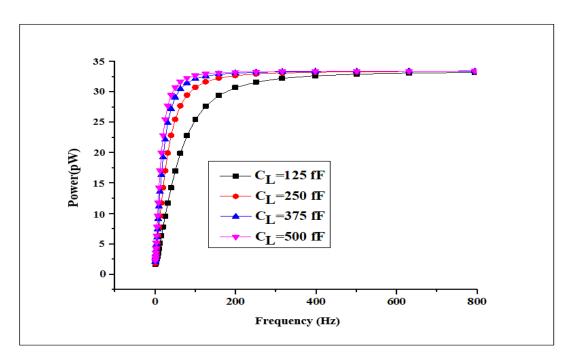

| Fig.7.22: Power consumption vs. load capacitor                                                                                           | 201 |

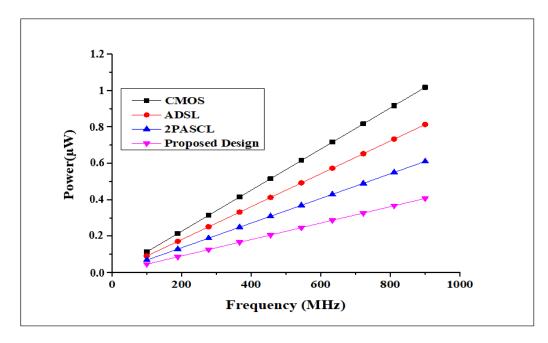

| Fig.7.23: Power consumption vs. lower operating frequency (up to 900MHz)                                                                 | 201 |

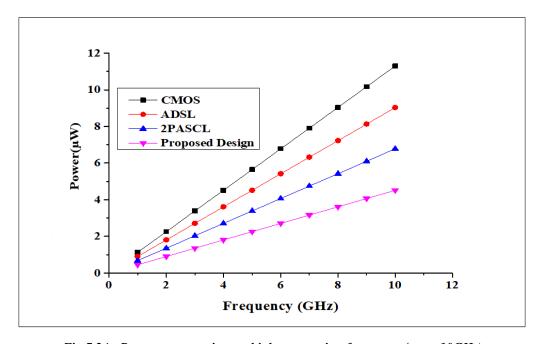

| Fig.7.24: Power consumption vs. higher operating frequency (up to 10GHz)                                                                 | 202 |

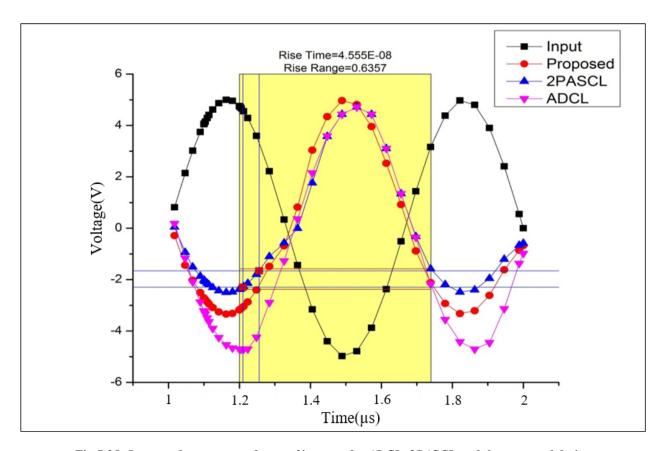

| <b>Fig.7.25:</b> Input and output waveforms of inverter for ADCL, 2PASCL and the proposed design                                         | 203 |

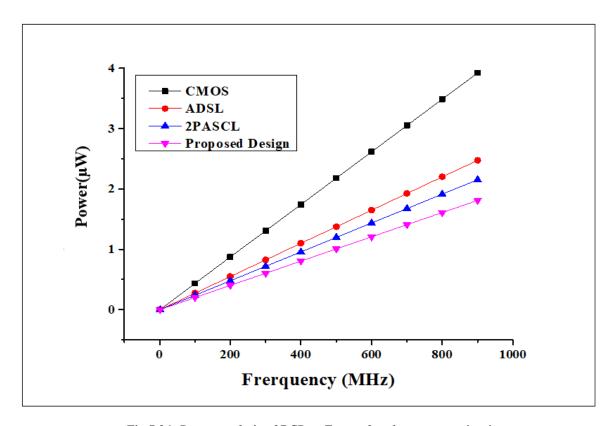

| Fig.7.26: Power analysis of BCD to Excess-3 code converter circuit                                                                       | 204 |

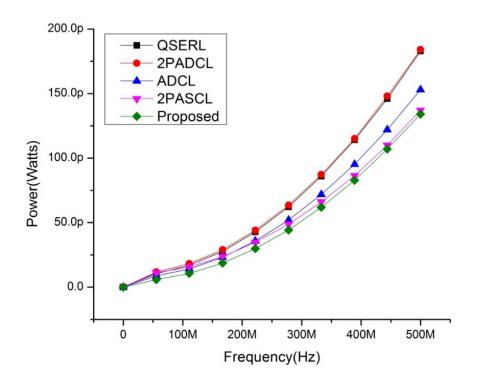

| <b>Fig.7.27:</b> Average Power Consumption of BCD to Excess-3 code converter circuit using 16nm_HP_PTM, within 5 clock cycles at 100 MHz | 206 |

#### **Abbreviation**

### A

ADCL Adiabatic Dynamic CMOS Logic

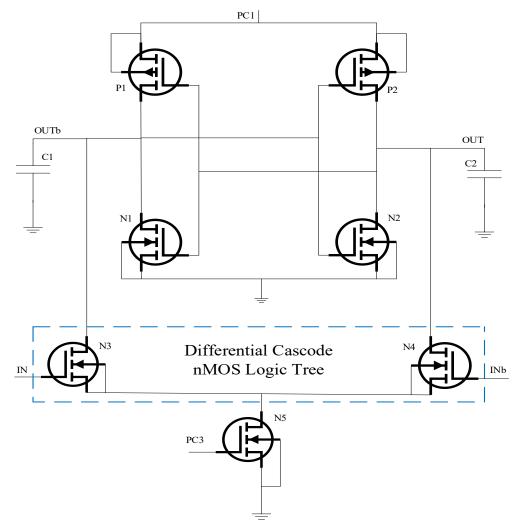

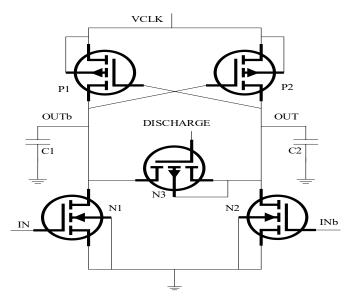

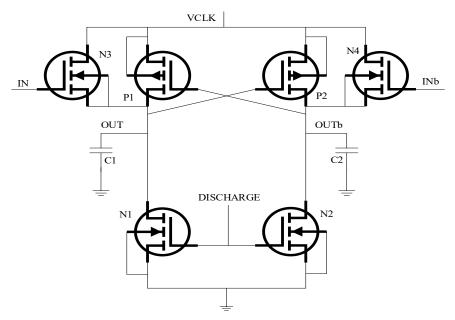

ADCVSL Adiabatic Differential Cascode Voltage Switch Logic

ADL Adiabatic Dynamic Logic

ALA Adiabatic Logic Array

ALU Arithmetic Logic Unit

APDL Adiabatic pseudo-domino logic

C

CAL Clocked CMOS Adiabatic Logic CCAL Clocked CMOS Adiabatic Logic

CDCAL Clocked Differential Cascode Adiabatic Logic

CEPAL Complementary Energy path Adiabatic Logic

CMOS Complementary Metal-Oxide-Semiconductor

CPAL Complementary Pass-Transistor Adiabatic Logic

CPU Central Processing Unit

CTGAL Clocked Transmission Gate Adiabatic Logic

D

DCPAL Differential Cascode Pre-resolve Adiabatic Logic

DFAL Diode-Free Adiabatic Logic Circuit

DTGAL Dual Transmission Gate Adiabatic Logic

E

ECRL Efficient Charge Recovery Logic

EEL Energy Efficient Logic

EFAL Energy-Efficient Adiabatic Logic

EPFAL Enhanced Positive Feedback Adiabatic Logic

G

GFCAL Glitch-Free and Cascadable Adiabatic Logic

H

HEERL High-Efficient Energy Recovery Logic

I

IAPDL Improved Adiabatic Pseudo-Domino Logic

IAPDL-2 Improved Adiabatic Pseudo-Domino Logic 2

ICAL Improved Clocked Adiabatic Logic

IDFAL Improved Diode Free Adiabatic Logic

IECRL Improved Efficient Charge Recovery Logic

IPGAL Improved Pass-Gate Adiabatic Logic

N

NERL NMOS Energy Recovery Logic

P

PAL Pass-transistor Adiabatic Logic

PFAL Positive Feedback Adiabatic Logic

PSAL Pre-resolve and Sense Adiabatic Logic

Q

QCA Quantum Dot Cellular Automata

QSERL Quasi-Static Energy Recovery Logic

QSSERL Quasi-Static Single-phase Energy Recovery Logic

R

REL Recovered Energy Logic

RERL Reversible Energy Recovery Logic

S

SCAL Source Coupled Adiabatic Logic

SCRL Split-level Charge Recovery Logic

SPGAL Symmetric Pass Gate Adiabatic Logic

SQAL Secured Quasi Adiabatic Logic

## T

TSEL True Single-Phase Energy Recovery Logic

2PADCL Two Phase drive Adiabatic Dynamic CMOS Logic

2PADL Two-phase adiabatic dynamic logic

2PASCL Two-phase clocked adiabatic static CMOS logic

2PC2AL Two-Phase Clocked CMOS Adiabatic Logic

2P-PFAL Two-Phase Positive Feedback Adiabatic Logic

#### CHAPTER-1

#### Introduction

#### 1.1. Background

The history of semiconductors is a attractive journey that has revolutionized the field of electronics. Since the discovery of the transistor in the mid-20th century, the semiconductor industry has undergone remarkable advancements. The foundations of semiconductor technology were laid in the early 20th century. In 1904, the physicist John Ambrose Fleming invented the vacuum diode, which allowed the unidirectional flow of electric current. This marked the beginning of active electronic components. Later, in 1947, William Shockley, invented the transistor, which proved to be a significant breakthrough in semiconductor technology. The transistor supplanted cumbersome vacuum tubes and facilitated the development of compact, more proficient electronic equipment (Bardeen & Brattain, 1948).

#### 1.1.1. Small-Scale Integration (SSI)

The concept of integrating multiple transistors onto a single semiconductor substrate emerged in the late 1950s. Jack Kilby created the first germanium-based integrated circuit (IC) in 1958. This initial IC, consisting of a few transistors and passive components, typically around 3 to 30 components, was the precursor to SSI technology. Simultaneously, Robert Noyce, from Fairchild Semiconductor, independently developed a comparable integrated circuit utilizing silicon. These ground-breaking developments set the stage for the rapid advancement of semiconductor technology (Kilby, 1964).

#### 1.1.2. Medium-Scale Integration (MSI)

The 1960s witnessed further progress in integrated circuit technology, leading to the birth of medium-scale integration (MSI). By using improved manufacturing processes and techniques, engineers were able to fit hundreds of transistors on a single chip, typically ranging from 30 to 100 components. In 1961, Fairchild Semiconductor introduced the first commercial IC, which contained multiple transistors, resistors, and capacitors. This development marked the transition from SSI to

MSI technology. MSI circuits found applications in various fields, including the military, aerospace, and early computers (Drummond, 2013).

#### 1.1.3. Large-Scale Integration (LSI)

As the semiconductor industry continued to evolve, researchers and engineers sought to increase the complexity and density of integrated circuits. Large-scale integration (LSI) emerged as a significant milestone in this pursuit. Gordon Moore, made the legendary prediction in 1965, which represents as Moore's Law. This observation became a driving force for the development of LSI technology (Moore, 1975; Dennard et al., 1974). The transition from MSI to LSI was facilitated by advances in semiconductor manufacturing processes, such as the introduction of planar technology and the use of photolithography. This marked the beginning of a new era where more complex circuits could be realized on a single chip.

#### 1.1.4. Very Large-Scale Integration (VLSI)

VLSI technology emerged in the late 1970s as a result of the desire to achieve greater degrees of integration and enhanced performance. VLSI technology marked a substantial advancement, enabling the incorporation of millions of transistors into a single die. This marked the birth of modern microprocessors and advanced digital systems (Abed & Siferd, 2003). The VLSI era was characterised by advancements in semiconductor fabrication processes, including the complementary metal-oxide semiconductor (CMOS) technology. It delivers reduced power usage, increased packing density, and improved performance, making it the dominant technology for VLSI designs. Additionally, computer-aided design (CAD) tools contribute significantly to the design and verification of complex VLSI circuits. By the 1990s, VLSI technology had become the foundation of modern computing, enabling the development of powerful microprocessors, memory devices, and system-on-chip (SoC) designs (White, 1982). The continuous progress in VLSI technology made it possible to realise ever more intricate and sophisticated electronic systems (Moore, 1975).

#### 1.1.5. Ultra-Large-Scale Integration (ULSI)

ULSI refers to the process of placing an extremely large number of transistors—typically millions or billions—onto a single integrated circuit. This technology is key to modern electronics, enabling compact, high-performance devices like microprocessors and memory chips. As ULSI

circuits become more advanced, challenges such as managing heat dissipation, reducing power consumption, and improving signal transmission efficiency arise. Recent innovations include the use of materials like copper and low-dielectric insulators to optimize performance. Additionally, research into new interconnect technologies, such as carbon nanotubes, aims to address limitations of traditional materials and further enhance the scalability and speed of ULSI circuits (Li et al., 2024; Shacham-Diamand, 2024).

#### 1.2. Problem Description

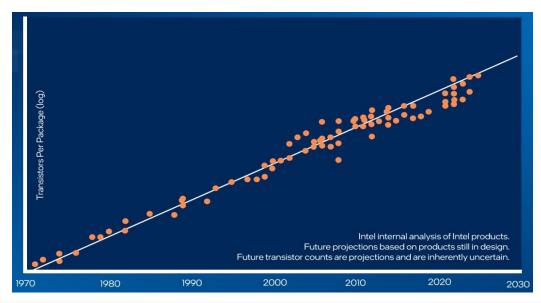

The history of semiconductors has witnessed remarkable advancements, from the innovation of the transistor to emergence of VLSI technology. The evolution from SSI to MSI, LSI, and ultimately VLSI has enabled the integration of an ever-increasing transistors on a single chip, resulting in electronic gadgets that are more compact, potent, and energy-efficient. According to Moorse's Law, a single chip can now contain billions of transistors. Due to the high number of transistors, ICs offer remarkable processing capabilities. The historical, contemporary, and projected device transistor counts are shown in Fig. 1.1. For the first 40 years, we were able to expand largely due to advancements in our manufacturing method. However, the increasing power density of these tightly packed IC chips prohibits designers from utilising these capabilities. Therefore, even though it is possible to place nearly a billion transistors on a single die, circuit designers for low-power applications cannot do so, as they are extremely limited by these power concerns (Rabaey, 1999).

Fig.1.1: Number of transistors per device: past, present, future (Intel Corporation, 2023)

#### 1.3. Motivation

The implementation of low-power design is of utmost significance in order to prolong the lifespan of batteries, particularly considering the constrained advancements in battery technology (Kuroda & Hamada, 2000). The prevalence of high-speed systems, including microprocessors, has become increasingly widespread, resulting in heightened power consumption, concerns over reliability, and the emergence of heat-related complications. The consideration of low-power design is of utmost importance for portable and high-performance systems since an increase in clock frequency leads to a corresponding rise in power dissipation. A range of methodologies, encompassing device features and algorithm selection are employed in order to mitigate power usage (Alioto, 2012). The development of integrated circuits has witnessed advancements in transistor density and enhanced switching rates, resulting in improved overall system performance. Nevertheless, the endeavour to achieve optimal performance has resulted in heightened power and energy dissipation, hence requiring more expensive cooling and packaging solutions (Bellaouar & Elmasry, 2012). It is anticipated that high-end microprocessors will consume a considerable amount of power in the future, thereby highlighting the imperative for the development of creative solutions aimed at reducing power consumption.

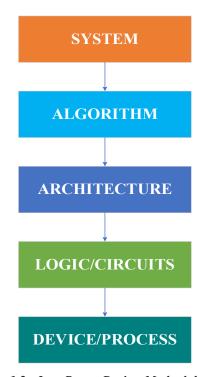

#### 1.4. Low-Power Design Methodology

To enhance digital systems' energy dissipation capabilities, it is crucial to incorporate low-power approaches across the whole design continuum, which encompasses the system-level as well as the process-level (Rabaey & Pedram, 2012). This task should be implemented with a simultaneous focus on maintaining optimal performance. In the context of this optimization quest, a basic prerequisite is a deep understanding of power distribution within a processor (Bearden et al., 1995). Therefore, it is crucial to carefully tune the individual components or modules that contribute significantly to power consumption to accomplish power conservation. Figure 1.2 illustrates a low-power design methodology across several hierarchical levels, such as system, algorithm, architecture, circuit, and device (Unsal & Koren, 2003). Every level of design is thoroughly examined in terms of its unique concerns, difficulties, and methodological methods. By incorporating these strategies, designers can achieve optimal power efficiency while maintaining the system's performance integrity. The dominant usage of portable gadgets and the growing prevalence of the occurrence of Internet of Things (IoT) have required the creation of energy-efficient VLSI

design processes. These methodologies are designed to extend battery life and attain maximum power optimization.

#### 1.4.1. System Level Design

The primary objective at the system level is to augment the overall power efficiency of VLSI system. Methods like dynamic voltage and frequency scaling (DVFS) are applied to modify operating voltage and clock frequency dynamically based on the system workload. Power management schemes like power gating and body-biasing are also used to minimise leakage power. Furthermore, system-level optimizations involve careful system partitioning and resource allocation to exploit parallelism and reduce power consumption (Unsal & Koren, 2003).

Fig.1.2: Low Power Design Methodology

#### 1.4.2. Algorithm Level Design

At the algorithm level, power optimization techniques aim to reduce computational complexity and data movement. Algorithmic modifications, such as algorithmic-level parallelism, can distribute the workload across multiple processing units, enabling power-efficient execution. Furthermore, we can optimize algorithms to minimize memory access, thereby reducing power

consumption. Techniques such as algorithmic pruning and approximation algorithms can trade off accuracy for reduced computational requirements and power consumption (Benini & Micheli, 2000).

#### 1.4.3. Architecture Level Design

At the architecture level, power optimization techniques involve designing efficient hardware structures that perform computations with minimal power consumption. Approaches such as instruction-level parallelism and pipelining exploit parallelism within the processor architecture to attain better throughput as well as increase power optimization (Raghunathan et al., 2012). To reduce power use, architecture-level improvements also include using energy-efficient interconnects, memory hierarchies that work well, and specialized circuits like application-specific integrated circuits (ASICs) (Chen & Kucukcakar, 1997).

#### 1.4.4. Circuit-Level Design

Circuit-level techniques focus on reducing power dissipation through circuit-level optimizations. These techniques rely on design strategies such as clock gating and voltage scaling to minimize dynamic power loss. Transistor sizing, power gating, and the use of low-leakage transistors are also employed to reduce leakage power (Macii et al., 1997). Furthermore, circuit-level optimizations consider the reduction of parasitic capacitance and resistance to minimize power dissipation (Rabaey & Rabaey, 2009).

#### 1.4.5. Device Level Design

At the device level, power optimization techniques aim to enhance the efficiency of individual transistors. These techniques include the utilisation of sophisticated process technology, like FinFET, which offers better control over leakage power and improved performance. Additionally, Kim et al. (2010) suggest using techniques like threshold voltage adjustment and advanced packaging technologies like through-silicon vias (TSVs) to lessen power usage. Low-power VLSI design is a multidimensional challenge that requires careful consideration at various design levels. System, algorithm, architecture, circuit, and device-level designs collectively contribute to achieving optimal power efficiency while maintaining system performance. By integrating these levels of design techniques, designers can achieve substantial power savings in VLSI systems for a wide range of applications. These strategies ensure efficient transistor operation, minimized leakage

power, and enhanced interconnectivity, resulting in comprehensive power optimization and improved energy efficiency.

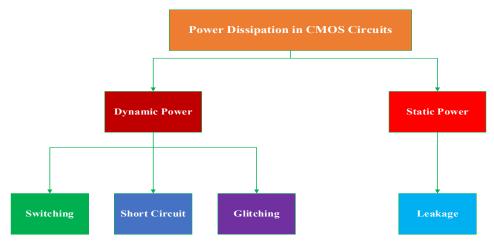

#### 1.5. Different Power Consumptions in Digital CMOS Circuit

In a CMOS circuit, the overall power consumption, denoted as,  $P_{total}$ , has two primary constituents: dynamic power, referred to as  $P_{dynamic}$  and static power, denoted as,  $P_{static}$ . Mathematically (Wiltgen et al., 2013):

$$P_{total} = P_{dynamic} + P_{static} \tag{1.1}$$

The term  $P_{dynamic}$  pertains to the electrical power used by a circuit while it is engaged in productive tasks during the active mode. On the other hand,  $P_{static}$  denotes the power dissipated, once the circuit is idle, known as leakage current (Rabaey, Chandrakasan, & Nikolic, 2003; Jan et al., 2003). Fig. 1.3 presents a comprehensive overview of the many categories of power use (Ng et al., 2022).

Fig.1.3: Classifications of Various Power Consumptions in CMOS Circuits.

#### 1.5.1. Dynamic Power Consumption

In CMOS, dynamic power dissipation refers to energy consumption as a result of the parasitic capacitors' charging or discharging energy, depending on the input of the logic circuits. This effect is observed during the process of transitioning between two logical states and is directly influenced by both the operating frequency and the magnitude of capacitance. The fundamental composition of dynamic power dissipation "includes three" distinct constituents (Liu & Svensson, 1994).

#### 1.5.1.1. Switching Power Consumption

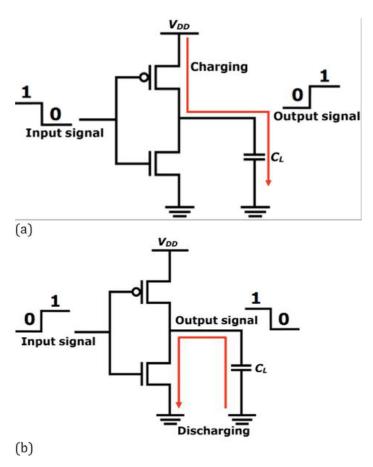

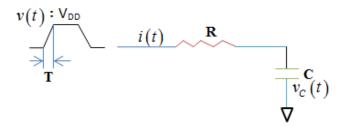

During the charging phase, as shown in Fig. 1.4(a), the output logic changed from a LOW to HIGH state because the PMOS and NMOS path transistors were ON and OFF, correspondingly. Current I(t) flows to the output capacitor  $C_L$  and, as a result, charges up and stores energy. This energy-stored  $E_D$  can be evaluated as given below (Ng et al., 2022).

$$E_D = \int_0^\infty i(t) \cdot V_{DD} dt \tag{1.2}$$

To get the capacitor voltage charged, the corresponding current is given as,

$$i(t) = C_L \frac{dV_{DD}}{dt} \tag{1.3}$$

Fig.1.4: CMOS inverter (a) Charging from VDD to CL (b) Dis-charging from CL to GND

$E_D$  in Eq. (1.2) can, therefore, be expressed as (Jan et al., 2003).

$$E_D = C_L V_{DD}^2 (1.4)$$

Therefore, it is possible to determine the energy  $E_C$  stored in  $C_L$  during each transition's charging phase as (Bartiromo & De Vincenzi, 2016),

$$E_C = \int_0^\infty i(t) \cdot v(t) dt = \frac{1}{2} C_L V_{DD}^2$$

(1.5)

i(t) represents the instantaneous charging current as a function of time during charging or discharging process. During charging, as depicted in Fig. 1.4 (a), i(t) is the current flowing from  $V_{DD}$  to the capacitor, and v(t) represents the instantaneous voltage across the capacitor  $C_L$  as a function of time during the charging process. Hence v(t) is voltage across the capacitor, which increases over time from 0 to  $V_{DD}$ .

Equations (1.4) and (1.5) illustrate the distribution of energy in a CMOS circuit. The phenomenon, known as switching activity, requires prioritizing Eq. (1.5) over Eq. (1.4) when evaluating switching power consumption. The main objective of Eq. (1.4) is to focus solely on an individual state transition. However, it is important to recognize that real-world situations often involve more complex interactions of signal changes at the circuit node. The complexity in question arises due to the possibility of many transitions occurring within a specified time span within the incoming signal. Therefore, in order to calculate the total delivered power, referred to as  $E_{Dt}$ , it is necessary to scale Eq. (1.4) by a factor N, which represents the total number of transitions. Consequently, (Pal, 2015)

$$E_{Dt} = N. C_L V_{DD}^2 \tag{1.6}$$

Consider a node within a circuit that alternates at a frequency  $f_{switch}$  throughout a period T, then N may be defined as,

$$N = T. f_{switch} (1.7)$$

From eq. (1.7) into eq. (1.6), the overall energy may be described as (Cutitaru, 2014).

$$E_{Dt} = T. f_{switch} C_L V_{DD}^2 (1.8)$$

Now switching power  $P_{switch}$  and total energy  $E_{Dt}$  can be characterized as,

$$P_{switch} = \frac{E_{Dt}}{T} \tag{1.9}$$

Using Eq. (1.8) into (1.9), we can write,

$$P_{switch} = f_{switch} \cdot C_L V_{DD}^2 \tag{1.10}$$

Equation (1.10) is applicable for precise computation of  $P_{switch}$ , provided that the assumption stated in Eq. (1.7) remains valid. In most CMOS circuits, it is crucial to recognize that the switching behaviour of logic components does not display a uniform frequency. Hence, it is more compelling to articulate the concept of  $f_{switch}$  in relation to the multiplication of AF and the clock frequency  $f_{clk}$  (Weste & Harris, 2015).

$$f_{switch} = AF. f_{clk} (1.11)$$

Therefore, Eq. (1.10) may be expressed as (Leblebici, 2004),

$$P_{switch} = AF. f_{clk}. C_L V_{DD}^2$$

(1.12)

The variable  $C_{dyn}$ , sometimes referred to as the dynamic effective capacitance, is used to denote the product of  $C_L$ , and AF, or  $(AF, C_L = C_{dyn})$ . Therefore, Eq. (1.12) may be reformulated as (Roy & Malik, 1994),

$$P_{switch} = f_{clk}. C_{dyn}. V_{DD}^{2}$$

$$\tag{1.13}$$

The probability of a circuit node moving from logic 0 to 1 state is the definition of the activity factor, (AF) given by Weste and Harris (2015). Hence, the inclusion of (AF) in the estimation of a circuit's power consumption has significant importance. The probability of a circuit node migrating to logic state 0, designated  $P_f^0$ , and logic state 1, designated  $P_f^1$ , can be multiplied to find the AF value for a circuit node exhibiting irregular switching patterns. When expressed mathematically, AF is,

$$AF = P_f^0 \times P_f^1 \tag{1.14}$$

As an illustration, consider an XOR-gate with the expression  $Y = A\overline{B} + \overline{A}B = A \oplus B$  for a switching function. Table 1.1 presents the function's truth table (Norouzi & Heikalabad, 2019). Only two of the four possible input values result in logic 1 at output Y, while the other two all result in logic 0, as depicted in the truth table. As a result, we may write  $P_f^{\ 0}$  as  $\frac{2}{4}$  and  $P_f^{\ 1}$  as  $\frac{2}{4}$ . Using these numbers in Eq. (1.14), we obtain a value for (AF) of 0.25. This means that there is just a 0.25

percent chance that the circuit is actually on. By contrasting this figure with the occurrence of a high state in the Boolean table, we are able to notice that the activity factor is an effective measure of the circuit's operational rate.

Table 1.1: Truth Table of XOR-gate

| Input |   | Output |  |

|-------|---|--------|--|

| A     | В | Y      |  |

| 0     | 0 | 0      |  |

| 0     | 1 | 1      |  |

| 1     | 0 | 1      |  |

| 1     | 1 | 0      |  |

#### 1.5.1.2. Short Circuit Power Consumption

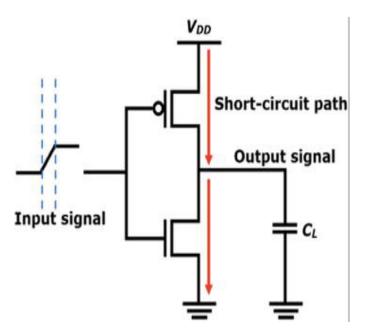

When loading and discharging the parasitic capacitance, the circuit delays its transitions in the logic state. Employing NMOS and PMOS transistors during switching events results in power loss due to short circuits. Both types of transistors conduct at the same time during logic state transitions, making a straight current channel from  $V_{DD}$  to ground. The short-circuit current going through the transistors thru the transitional stage as depicted in Fig. 1.5. This characteristic renders the operation inefficient and unpredictive. The mathematical expression for short-circuit power, symbolized as  $(P_{short})$ , can be obtained using the following derivation (Veendrick, 1984).

$$P_{short} = T_{sc}.V_{DD}.I_{peak} (1.15)$$

The parameter  $T_{sc}$  represents the duration of the ascending or descending edge of the input signal, while  $I_{peak}$  corresponds to the peak current. The estimation of  $I_{peak}$  can be inferred from the characteristics of the transistor, such as its dimensions and the technological technique used (Nose & Sakurai, 2000).

Fig. 1.5: Graphical representation of short-circuit path in CMOS inverter.

#### 1.5.1.3. Glitching Power Consumption

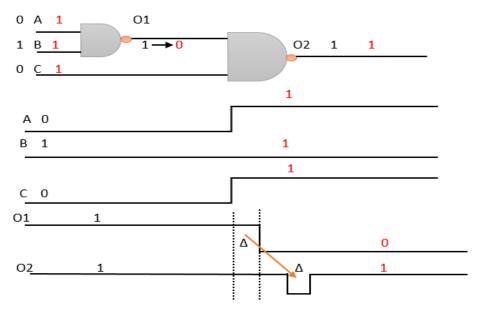

The term "glitches" refers to short and unintentional aberrations in the logical states present within a digital circuit (Raghunathan et al., 1996). The presence of these events can be attributed to a range of causes, encompassing signal reflections, noise coupling, and inherent delays in signal transmission. When a fault arises, it triggers temporary shifts between logical states, resulting in the production of dynamic power dissipation within the CMOS circuit (Choi et al., 2001). It is well acknowledged that in real-world applications, every logic gate demonstrates finite delays, resulting in the manifestation of glitches as a consequence of these intrinsic delays. When the input variables A, B, and C change from 010 to 111, as shown in Fig. 1.6, the associated output values exhibit the following evolution: Initially, with input values 0 and 0, the respective output values are O1 = 1 and O2 = 1 (Safaiezadeh et al., 2021). Nevertheless, when the input is modified to 111, the resulting output undergoes a transformation such that O1 becomes 0 and O2 becomes 1. In all instances, it is assumed that an ideal scenario is present, wherein gate delays can be considered insignificant. Nevertheless, the incorporation of gate delays results in divergent consequences. The inclusion of gate delays in output replies becomes necessary when even a slight delay is present, resulting in the occurrence of glitches (Raghunathan et al., 1999).

Fig. 1.6: Transition of signals through logic gates

Fig.1.7: Reduction of glitching using gates